(2)高速数据读流程:①NAND Flash芯片激活异步读写状态;②从逻辑控制模块获取读取页地址;③向NAND Flash芯片发送读操作命令;④向NAND Flash写入多操作操作地址;⑤读取NAND Flash数据发送到逻辑控制模块中;⑥当数据读完一页后,重复步骤②~⑥。

4 实验测试

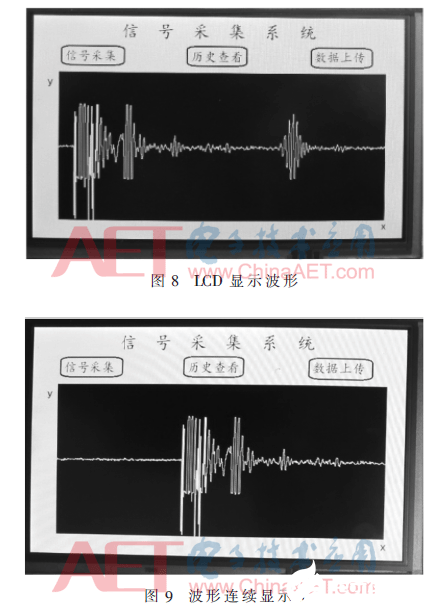

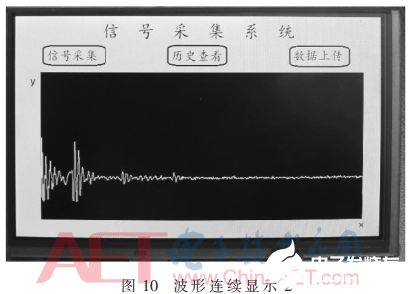

测试平台由超声发射电路、超声接收电路、超声探头和有焊缝的金属薄板构成。超声探头发射2.5 MHz的超声信号到金属薄板。当超声信号到达焊缝部位时,信号发生部分或全部反射,产生回波信号。信号采集系统通过超声接收电路采集回波信号,经过逻辑控制模块处理后,写入存储模块。同时,经过处理的数据通过LCD显示屏进行显示。图8为信号检测系统输出波形。对比两个波形发现,系统能够以50 MHz的采样率进行良好的采样。图9和图10为连续采样数据波形输出,实现了连续多批次信号采集。

5 结束语

本系统通过AD9226高速模数转换模块,将采集到的模拟信号转换为数字信号,经过FPGA存储到大容量NAND Flash中,并在LCD显示屏中显示波形。在实际应用中,该系统能够进行持续长时间的多批次高速信号采集,并具有小型化、易于携带的特点。

参考文献

[1] 张晓威,苏淑靖。基于FPGA的高速高精度数据采集系统的设计[J]。仪表技术与传感器,2016(1):70-72.

[2] BAO S,YAN H,CHI Q,et al.FPGA-based reconfigurable data acquisition system for industrial sensors[J].IEEE Transactions on Industrial Informatics,2017,13(4):1503-1512.

[3] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J]。电子与信息学报,2010,32(3):714-727.

[4] XU Z,ZHU L,SHAN J F,et al.A new high-speed data acquisition system[J].Journal of Fusion Energy,2015,34(3):1-4.

[5] 黄远望,严济鸿,周伟。基于FPGA的数据采集测试系统设计[J]。现代雷达,2015,37(4):73-76.

[6] KHEDKAR A A,KHADE R H.High speed FPGA-based data acquisition system[J].Microprocessors & Microsystems,2016,49:87-94.

[7] 李茂,杨录,张艳花。基于FPGA和USB的多通道超声检测系统设计[J]。仪表技术与传感器,2017(8):82-84.

[8] 孟晓东。基于FPGA的DDR3控制器设计与验证[D]。长沙:国防科学技术大学,2012.