FPGA采用Xilinx公司Spartan-3E系列的XC3S1200E,它有120万系统门、136 kB分布式RAM、504 kB块RAM、8个数字时钟管理模块(Digital ClockManager,DCM)、最大可用I/O数为304。其内部资源以及管脚数量能够满足本模块的设计需要。本模块用两种方式配置FPGA,在调试中使用JTAG口配置,在最终产品中使用PROM配置,选用XCF04S芯片。

MXP-123MD-F是HC Genuine公司生产的一种支持热插拔的高速小型光收发模块,用于光电转换,其信号传输率为622 Mbit·s-1,输入输出电平为差分LVPECL电平。在光纤数据接收端通过MAX9376将信号转换为LVDS电平后再通过串并转换器SN65LV1224B送至FPGA。FPGA将采集数据输出给并串转换器SN65LV1023A后经过MAX9376转换为LVPECL电平再通过光纤发送出去。

3 软件设计

FPGA编程软件为Xilinx公司的ISE,分别采用原理图方式和VHDL硬件编程语言编写,顶级文件为原理图方式。

时钟的管理与控制采用DCM模块实现。DCM的功能包括消除时钟的延时、频率的合成、时钟相位的调整等;并能映射到PCB上,用于同步外部芯片,将芯片内、外的时钟控制一体化。在模块设计中,DCM将晶振提供的40 MHz时钟信号,经频率合成为12 MHz、60 MHz时钟进行逻辑处理;并将时钟映射在PCB上用于同步并串转换器。

数据的缓存使用双口RAM,利用FPGA内部的逻辑资源实现。其中大容量的缓存使用块RAM,使用它们可以达到较高的读写速度,同时不会占用逻辑资源。小容量的缓存使用分布式RAM。

8B/10B编码技术具有很好的直流平衡特性,具有一定的抗干扰和检错能力,适用于高速串行光纤传输系统。它将8 bit的基带数据按照3B/4B和5B/6B两个编码映射成10 bit的数据进行发送,防止在基带数据中有过多的0码流或1码流,保证输出码流的直流平衡。该技术能够有效地检测错误;提供有效的比特变化密度用于时钟恢复;可以抵抗较差传输信道的干扰;实现相对简单,以廉价的方式制造可靠的收发器。

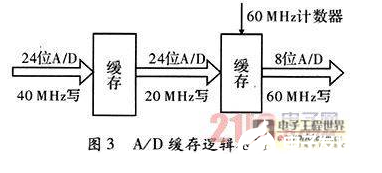

FPGA的逻辑框图如图2所示。输入数据包括8组12位的A/D数字信号;串并转换器的输出恢复时钟及10位并行数据;上位机发送的采样导前信号(DQ)以及采样时间长度信号(ES)。FPGA的输出数据包括4路并串转换器的参考输入时钟及4组10位的并行信号。