3 工程应用及性能测试

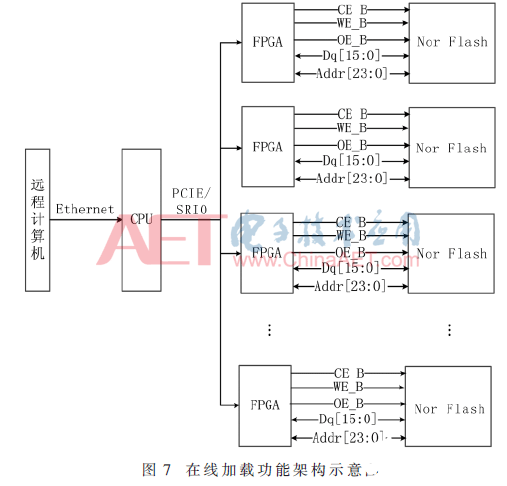

以一实际项目工程为例,系统中具有10块FPGA进行程序更新,其在线加载功能系统架构如图7所示。

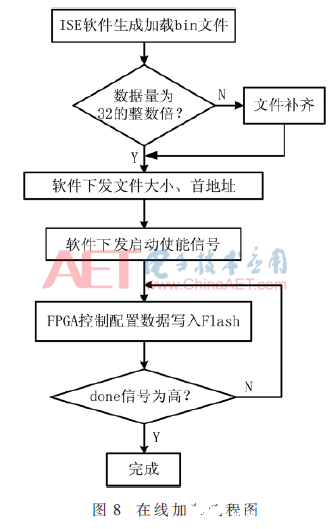

系统主控CPU运行在Linux系统下,CPU通过以太网与远程计算机进行通信调试,同时通过PCIE或SRIO高速总线向每块FPGA下发配置数据,最后再由Flash控制器完成数据的写入。如前文所述,一次写缓冲操作的数据量为32个字,而配置文件的大小有可能不是32个字的整数倍,所以还需要应用软件对配置文件进行补齐操作。单个FPGA在线加载流程简要叙述如图8所示。

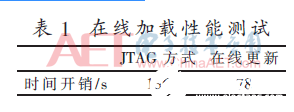

更新单块FPGA程序时,以一实际测试的3.47 MB大小的配置文件为例,经FPGA在线更新程序固化的时间和使用ISE14.7软件JTAG方式固化的时间如表1所示。

Flash芯片手册中给出的典型擦除和写缓冲时间分别0.5 s和480 μs,则可计算出理论上3.47 MB大小的文件固化所需的典型时间约为41 s。由于器件等因素影响,实测时用时往往大于该时间,但总体来说,使用在线更新方式的耗时要比用JTAG方式耗时更少。

而当更新系统中的10块FPGA时,由于每块FPGA均可同时进行在线更新操作,程序固化所消耗的时间与单块FPGA程序更新时间开销大致相当,可见并行在线更新方式相较于传统JTAG方式无疑可以大大缩短时间。

4 配置文件不断电加载和备份方法

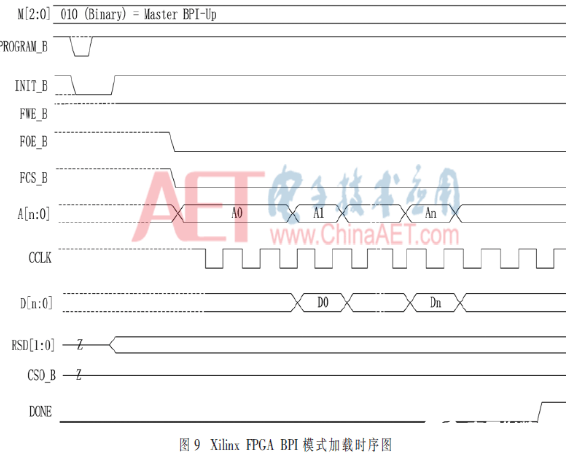

每次更新完配置之后,通常做法是对FPGA进行断电重启实现重新加载,但工程应用时断电可能会影响系统其他模块的正常工作。为使FPGA在不断电的情况下自动加载更新完的配置程序,可通过配置FPGA芯片的PROGRAM_B信号来实现,BPI模式下的时序如图9所示。

考虑到若在配置过程中FPGA发生断电等异常,则Flash中的配置文件损坏,FPGA将无法实现加载,需要重新使用JTAG方式烧写配置文件。为防止该种情况发生,可分配Flash的一块区域用于备份配置文件,发生FPGA无法正常加载的异常时,可读取该备份配置文件实现FPGA再次正常加载,但前提是该部分Flash存储空间预先固化了带有FPGA在线更新功能的程序。