CX = 1.0 Uf Cy = 3300PF EMI等級 : Fcc Class

Type : Ac Common Mode Choke

Step 1:电感(L)确定:

由电路图可知共模信号由L3和C2、C3组成的共模滤波器抑制,实际L3与C2和C3构成两路LC串联电路,分别吸收L和N在线的噪声。只要确定滤波电路的截止频率,也已知电容容量C,则可以下式求出电感L。

fo= 1/(2π√LC)L → 1/(2πfo)2C

通常EMI测试频宽如下:

传导干扰:150KHZ →30MHZ(注:VDE标准10KHZ - 30M)

辐射干扰:30MHZ 1GHZ

实际的滤波器无法达到理想滤波器那样陡峭的阻抗曲线,通常可将截止频率设定在50KHZ左右。在此,假设f o = 50KHZ,则

L =1/(2πfo)2C = 1/ [( 2*3.14*50000)2 *3300*10-12] = 3.07mH

L1、L2、C1组成(低通)常模滤波器,线间电容有1.0uF,则常模电感为:

L = 1/ [( 2*3.14*50000)2 *1*10-6] = 10.14uH

如此,可得到理论要求的电感值,若想获得更低的截止频率fo,则可进一步加大电感值,截止频率一般不低于10KHZ。理论上电感量越高对EMI抑制效果越好,但过高的电感将使截止频率更低,而实际的滤波器只能做到一定宽带,也就使高频噪声的抑制效果变差(一般开关电源的噪声成分约为5 ~10MHZ间,但也有超过10MHZ之情形)。另外,电感量愈高,则绕线匝数愈多,或CORE之ui越高,如此将造成低频阻抗增加(DCR变大)。匝数增加使分布电容也随之增大(如图4),使高频电流全部经此电容流通。过高的ui使CORE极易饱和,同时制作也极困难,成本也较高。

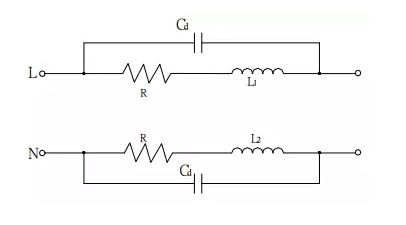

图4有分布电容Cd之等效电路图

Step 2 CORE材质及SIZE确定

从前述设计要求中可知,共模电感器需不易饱和,如此就需要选择低B - H角形比之材料,因需要较高的电感值,磁芯的ui值也就要高,同时还必须有较低的磁芯损耗和较高的Bs值,符合上述要求之CORE材质,目前以Mn - Zn铁氧体材料CORE最为合适。

COEE SIZE在设计时并无一定的规定,原则上只要符合所需电感量,且在允许的低频损耗范围内,以所设计的产品体积最小化即可。

因此,CORE材质及SIZE提取应以成本、允许损耗、安装空间等作考察。共模电感常用CORE之ui约在2000 ~ 10000之间。Iron Powder Core也有低的铁损,高的Bs和较低的B - H角形比率,但其ui较低,故一般不被应用于共模电感,而该类磁芯却是常模电感器之优选材料。