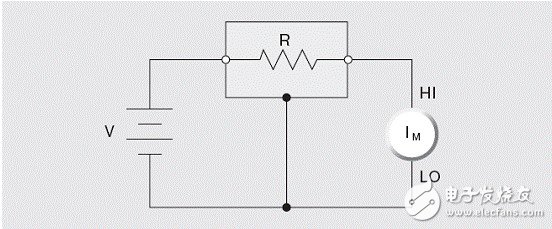

图2是一个屏蔽的例子。用导电材料制成的屏蔽总是连到静电计或皮安计的低阻抗输入端,或者连到SMU的LO输出端(或公共端)。如果电路LO端对地浮空,则要采取特别的安全措施,避免人员触及该屏蔽。

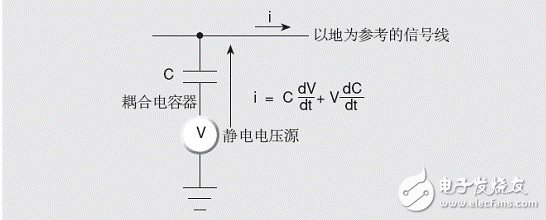

仪表HI端和被测装置之间的电缆也需要屏蔽。用连接到LO端的金属屏蔽将信号导体包围起来,可以大大降低静电噪声源和信号导体或电缆之间的电容耦合,如图3所示。有了这种屏蔽,由静电电压源和耦合电容产生的噪声电流就经过屏蔽流到地,而不再流过信号线。

总的说来,遵守下列指导原则能够尽量降低静电耦合产生的电流:

* 使所有带电物体(包括人员)和导体远离测试电路的敏感区域。

* 在测试区域附近避免运动和振动。

* 当测量电流小于1nA时,将被测装置用金属闭合物包围屏蔽起来,并将该闭合物连到测试电路的公共端。

屏蔽和保护

屏蔽通常意味着使用金属的闭合物来避免静电干扰影响高阻抗电路。而保护意味着使用保持在与高阻抗电路相同电位的附加的低阻抗导体来阻止可能的干扰电压或电流。保护措施不一定提供屏蔽。

关于EMC,EMI设计就介绍完了,您有什么想法可以联系小编。