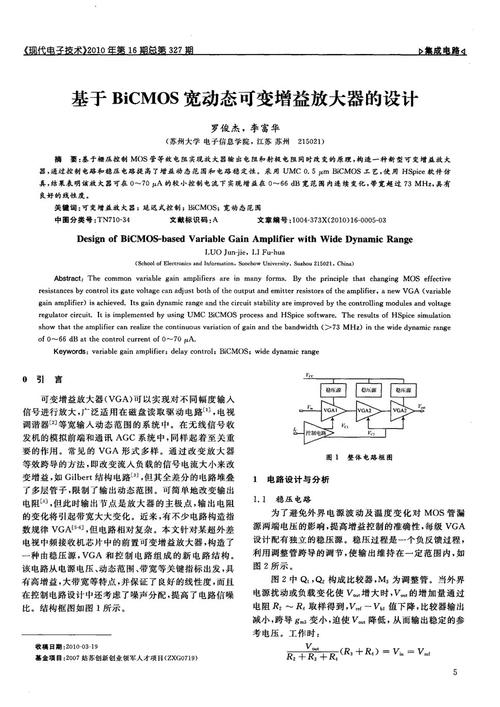

今天小编要和大家分享的是BiCMOS工艺分类 BiCMOS高速电路的设计考虑,接下来我将从BiCMOS工艺分类,高速BiCMOS电路的设计考虑,BiCMOS的应用,BiCMOS的基本器件,这几个方面来介绍。

BiCMOS工艺技术是将双极与CMOS器件制作在同一芯片上,这样就结合了双极器件的高跨导、强驱动和CMOS器件高集成度、低功耗的优点,使它们互相取长补短、发挥各自优点,从而实现高速、高集成度、高性能的超大规模集成电路。

BiCMOS工艺分类

BiCMOS技术是将单、双极两种工艺合适地融合在一起的技术,但这绝不是简单、机械地掺和在一起,很多工艺可以一块儿或设法结合在一起做。目前BiCMOS工艺主要有两种:一是以CMOS为基础的BiCMOS工艺,这种工艺对保证CMOS器件的性能较为有利;二是以双极工艺为基础的BiCMOS工艺,这种工艺比较张扬BJT器件的性能。

高速BiCMOS电路的设计考虑

1)双阱结构中的阱结构尺寸及其埋层

对BiCMOS电路来说,需要仔细研究CMOS阱和BJT器件的集电极的工艺要求。一个主要的工艺设计折衷方案涉及到外延层和阱的轮廓特性。对于BJT器件,一方面集电极-发射极之间的反向击穿电压U(BR)CEO、集电极,以及生产工艺的可控制性决定了外延层的最低厚度;另一方面,如果外延层太厚,特征频率fT就会下降而集电极电阻RC值就会增大。对于MOS器件,在制作pMOS器件时使用N+埋层就要求外延层必须足够厚,以避免过大的结电容和pMOS器件的背偏置体效应(back-biasbodyeffect)。

双阱结构中的N阱不仅影响pMOS器件,而且也可作为NpN型BJT器件的集电极。因此,除了应充分保证CMOS器件的性能以外,N阱掺杂既要足够重以防止Kirk效应(Kirkeffect),同时又应足够轻,以增高BJT器件的U(BR)CEO。

2)外延层与自掺杂

在两种类型的埋层上生成轻掺杂的薄外延层,对外延沉积工艺来说是一种挑战。必须使在垂直和水平方向的两种类型杂质的自掺杂尽量地小,以避免在阱中需要过量的反掺杂。

3)利用杂质离子注入降低MOS器件阈值电压

在pMOS器件的沟道区通过硼离子注入调节,降低其阈值电压;制作NMOS器件沟道区时注入磷离子,不仅可使NMOS器件的阈值电压分散性大为减小,而且还可减小N阱同p型衬垫的掺杂浓度比值。这一技术意味着N阱区掺杂浓度可以降低,因而NMOS器件的阈值电压大为减小,结果使通信用BiCMOS电路可在低电源电压(3.3V)下工作。

4)用硅栅自对准工艺减小交叠电容

制作MOS器件时采用硅栅自对准(在栅下源、漏区极少扩展)工艺,使栅-源和栅-漏扩散区的重叠大大减小,栅-源及栅-漏交叠电容相应地大为减小。这样做有利于硅栅双阱BiCMOS电路的工作速度得以提高。此外,硅栅自对准工艺也可明显减小设计同样沟长的MOS器件所需要的版图尺寸,因而芯片的集成度得到了提高(大约提高30%)。

5)用高电阻率p型硅衬垫来提高工作速度

BiCMOS器件应采用高电阻率p型硅衬垫,这样既与CMOS、射极耦合逻辑电路(ECL)和砷化硅(GaAs)工艺有良好的兼容性,又降低了NMOS器件的结电容,有利于提高通信和信息处理用BiCMOS电路的速度。

BiCMOS的应用

用于蜂窝电话和pDA的多功能电源管理

多电压电源管理

汽车电源管理器件

智能电池组

用于电信和数据通信卡的电压调节器

用于医疗产品的高精度A/D转换器

BiCMOS的基本器件

MOS管

(1)以双极工艺为基础的双阱BICMOS工艺下的MOS管结构:p沟器件做在N阱中,N沟器件做在p阱中.该工艺采用pN结对通隔离技术,有N+及p+双埋层结构,并采用薄外延层来实现器件的高截止频率和窄隔离宽度.其中NMOS管的源漏与NpN管的发射区和横向pNp管及纵向pNp管的基区接触扩散同时进行.pMOS管的源漏区扩散与NpN的基区扩散,横向pNp管的集电区,发射区扩散,纵向pNp管的发射区扩散同时完成.MOS管的工作原理与CMOS工艺下的管子一样.

(1)NpN管NpN晶体管是双极集成电路中的基本器件,以N外延层为集电区,Basep为基区,在Basep中做一重掺杂的N+为发射区.由其剖面图可见,NpN存在寄生的pNp,但是这个寄生的pNp不是在任何情况下都起作用.在模拟电路中,由于NpN管一般都处于截止或正向工作区,VBC-NpN<0,所以寄生pNp的发射结是反偏的,因为VBE-pNp=VBC-NpN<0,因而寄生pNp管截止.而在数字电路中,NpN工作在饱和区或反向工作区,此时VBE-pNp=VBC-NpN>0,寄生pNp将处于正向工作区,这将使相当大的一股反向NpN管的"发射极电流"变成无用电流流入衬底.所以在数字电路中要注意减小寄生pNp效应.一般工艺上通过掺金工艺和埋层工艺来减小寄生pNp正向运用时的共基极短路电流增益aSF.从而减小寄生pNp管的影响,增加有用电流的比值.

在实际的双极工艺中,除了寄生三极管外,还有无源寄生效应如串联电阻,寄生电容等,这些都将不可避免的影响到的电路的性能,下面做简要介绍,以便将来在版图设计过程中适当减小这些寄生效应.作为VNpN管存在三种寄生电阻:发射极串联电阻,集电极串联电阻,基区电阻.首先,发射区电阻由发射区体电阻和发射区接触电阻组成,一般发射区做成方形其长宽比相当小,所以电阻可忽略.接触电阻由发射区接触孔面积和硅与发射极金属的欧姆接触系数决定,所以小电流情况下,发射极的串联电阻是很小的可以忽略.第二是集电极串联电阻,相对来说比较大,在工艺上可以通过加埋层和深N+集电极接触扩散方法来减小;在版图设计时,可以采用双集电极或马蹄型集电极图形来减小,但此方法会增大寄生电容.第三,基区电阻主要由外基区(发射区扩散边缘到基极接触孔边缘),内基区(发射区扩散层下面的那部分基区)电阻和基极接触电阻.在版图设计上用双基极条或梳状电极以减小基区电阻.NpN管中的寄生电容主要有pN结的势垒电容和扩散电容.

(2)LpNp管

集成电路的模拟电路中常用到pNp管,如运放的输入极,输出极的有源负载等.一般情况下由于要与NpN管的制造工艺兼容,所以作出的pNp管的β小,fT低,临界电流小.是双极双阱工艺下的横向pNp管,此三极管也存在寄生的VpNp,解决办法是,一,版图设计时减少发射极面积与周长比,一般使用窄条形发射极.而下图的版图设计采用圆形发射区的设计,是为了减小表面复合的影响和获得均匀的表面横向基区宽度.而集电区设计成包围发射区的形式,是为使集电区尽可能多的收集到从发射区侧向注入的空穴.二,在工艺上采用增大结深及采用埋层工艺等办法.

(3)VpNp

LpNp的β,fT,ICr(临界电流)都小,只能用于小电流的情况,而衬底pNp,即VpNp则可以用于大电流.但在CMOS工艺介绍时说过,衬底pNp的应用有局限性,因为其集电区是电路的公用衬底,必须接低电位.衬底pNp管还存在较大的集电极串联电阻和集电结电容.所以一般将集电极接触窗口放在与之靠近的隔离槽上,这样可以避免但集电极电流较大时在衬底产生大压降,导致电路的其他地方的衬底外延变成正偏而破坏电路的正常工作.为了扩展VpNp的应用,在双极双埋层工艺下可以制作自由集电极VpNp,它共进行三次p型杂质的扩散:p-BL下隔离扩散;p+上隔离扩散,并作为深p+集电极;p型发射区扩散.由于在外延及上隔离的过程中p-BL埋层分上推距离大于N+-BL上推的距离,于是在p发射区下形成p型集电区.此结构的缺点如下:

(1)有效基区由外延层厚度,结深和埋层上推距离决定,所以控制精度较差.

(2)工艺步骤多.(3)版图尺寸大,影响成品率.

三,电阻

除了CMOS中介绍的四种电阻外,在双极工艺下还会有以下两种电阻:BASEp电阻和RI电阻(离子注入电阻),Bp电阻直接做于外延上,两端进行p+扩散,以获得欧姆接触,作为电阻的引出端.电阻体从p+扩散的边缘到边缘.其薄层电阻在200~600欧/方,Bp电阻的缺点是,其阻值受基区的影响.RI电阻是在外延层上注入硼离子形成电阻区,在电阻区的两端进行p扩散做为电阻的引出端.其薄层电阻0.1~20K欧/方,是电阻中精确度较高的一类电阻(可以达到10%),常做高精度要求的高阻.其温度系数TCR与退火条件及RS有关,可以控制,通常可以达到10-4以下.缺点是注入的结深较小(0.1~0.8vum),注入层的厚度受耗尽层的影响较大,导致压差大时会由于结深浅而被击穿.

关于BiCMOS,电子元器件资料就介绍完了,您有什么想法可以联系小编。