今天小编要和大家分享的是数字锁相放大器结构 数字锁相放大器原理,接下来我将从数字锁相放大器的结构,数字锁相放大器的原理,数字锁相放大器相对模拟锁相放大器的优势,数字锁相放大器新进展,这几个方面来介绍。

数字锁相放大器是一种用数字信号处理的方式实现的相敏检波器(或同步解调器)来构成的锁相放大器,数字锁相放大器比模拟锁相放大器有许多突出的优点而倍受青睐,成为现在微弱信号检测研究的热点。

数字锁相放大器的结构

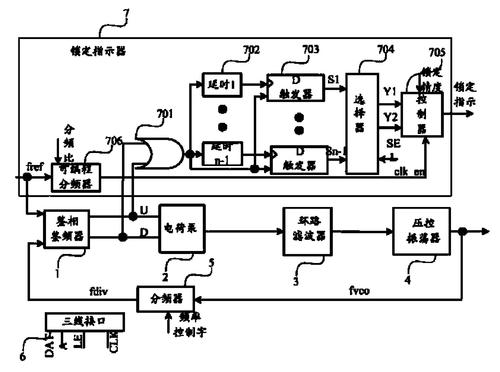

数字锁相放大器的原理如图所示。一般的结构包括以下一些部分,即信号输入通道、参考输入通道、数字相敏检波器、正交数字相敏检波器、数字低通、输出通道、辅助输入通道、输出微处理器、辅助输出通道和微控制器部分。

数字锁相放大器的原理

数字锁相放大器的信号的输入通道与模拟锁相放大器相同,只不过是交流放大必需保证转换为数字信号时有足够大的幅值。抗混叠滤波器是模拟信号数字化之前所要考虑的,其作用是滤除不需要的频率信号,并将要数字化的信号在不失真前提下将其频率上限限制在采样频率的一半以下,避免ADC的信号出现虚假信号,即主ADC的采样频率必须满足采样定律。被转换后的数字信号被送入数字信号处理器(DSp)中,依据一定的算法完成相敏检波器的功能,再通过数字低通滤波器后获取差频后的直流信号。参考通道以信号输入通道相同的采样速率提供数字相敏检波器所需要的相位信息,参考输入通道同样有内部和外部参考信号两种。在外部参考信号模式下,输入的模拟参考信号或逻辑电平,被一个DSp单元采用数字锁相环算法测量其频率,并产生所需要的相位信号。在内部参考信号的模式下,只需要给参考DSp单元输入所需要的参考信号频率值,就可以在所选定的频率上产生数字相敏检波处理单元所需要的相位信号,这种方式不需要外部参考信号和模拟锁相放大器所需要的相位锁相环,因此不需要时间锁相就可直接输出相位信号,降低了相位噪声。参考通道中的n倍频器不仅可以在与输入信号相同的频率上进行锁相,而且还可以在输入信号的n倍谐频上进行锁相检测,这在俄歇光谱学等领域中是非常有用的,但是n倍频后最大频率是受最大参考频率限制的。参考信号处理单元也可实现数字参考相移,其精度可达到毫度。同相相位和正交相位信号在数字处理单元中一般通过查询的方式实现,可以使同相相位信号和正交相位信号同时提供给两个数字解调器,使输出的两个分量能同步输出。输出通道中的数字低通滤波器,可以减小模拟滤波器的截止频率不稳定所造成的误差。输出DAC将数字信号转换为模拟信号输出,输出处理单元可以通过和的平方根算法和除法算法计算出被测信号的幅值和相位。输出微处理器可以对从辅助ADC的数字信号进行必要的运算,在通过DAC转换为模拟信号输出或数字显示。另外DLIA还包括一个微控制器,该微处理器有辅助数字输出、数字显示,键盘通讯,IEEE-488通讯和RS233通讯功能。

数字锁相放大器相对模拟锁相放大器的优势

(1)由于数字锁相放大器在输出通道中没有直流放大器,可以避免直流放大器的工作特性随时间变化的不稳定性和由于温度变化引起的温度漂移带来的干扰,这是模拟锁相放大器不可解决的问题之一;

(2)数字锁相放大器的内部晶振时钟源随时间和温度变化小,用这种稳定性高的时钟源来做调制信号和参考信号能降低参考信号的不稳定所带来的误差,同时在内部参考模式中,数字信号处理单元能在最短时间甚至能不需要延时就能完成锁相功能,尤其在频率扫描测量中有其明显的优点;

(3)如果被测信号有较强的正交性,采用数字锁相放大器的高性能的正交解调技术,使微弱信号检测精度能得到很大程度上的提高;

(4)随着技术的发展,数字信号处理单元的性价比提高,使数字锁相放大器的性价比也得到相应的提高,数字锁相技术将会更深入地影响未来的测量技术。

数字锁相放大器新进展

1。基于单片机的DLIA

目前通用单片机一般是8位型单片机,工作频率最大为20MHz。随着单片机技术的进一步发展,也逐渐出现了16位型单片机,工作频率也逐渐提高到100MHz。由于单片机的廉价和开发的便利性,使单片机将广泛地应用于DLIA。但是受到单片机处理能力的限制,因此用单片机的DLIA的算法要进行优化,使算法更加简单,有效并适合单片机的硬件特性。

文献6报道了由DDC112和At89c82528位单片机构成的DLIA。主要目的是用来测微弱的缓慢变化的光信号,由于背景光比较强,因此需要DDC112作为20位的ADC,来提高探测系统的动态范围。该系统的最大采样频率是2kHz,这主要受DDC112的采样速度限制。At89c8252限制了系统的运算能力,需要高效的优化算法来完成数字锁相放大功能。

作为LIA首要解决的问题是如何消除低频噪声,现在大多采用一种叫频谱倒置的算法。这种算法主要是通过交替交换采样点的正负号,实现比较简单,便于单片机处理。文献报道了一种适合于8位单片机的低通滤波算法,这种算法是单极点的2.5Hz的Butterworth低通滤波器,此算法的主要优点是滤波器的系数是1/256的倍数,可以通过简单的移位操作即可完成系数的除法运算。将上述两个算法融合与一起,即同时完成频谱倒置和低通滤波器的作用,其数学表达式如下

在实现过程中,由于采样数据是20位数据,中间运算数据要采用32位才能保证其精度,这要用四个字节才能完全表示,并且在读写存储器过程中也比较困难,这主要使用了C或C++中的枚举数据结构来解决的。另外文献还报道了通过数字查表方式修正由于系统中DDC112的两个不匹配积分电容所带来的误差[5],从而保证了系统的最大动态范围,提高了系统性能。

这样简单的系统之所以能取得较好的性能,主要用了优化的算法和通过数字查表方式得到解决。但是该系统由于单片机较差的处理能了和较慢的运行速度,使该系统只能应用于低频信号检测中。

2。基于专用DSp的DLIA

自从专用DSp诞生以来,使信号的数字实时处理成为可能。这主要得益于DSp中的乘加求和的快速运算功能,使复杂的算法能在几个指令周期内完成。DLIA的相关运算和数字滤波算法正是DSp的优势所在。文献报道了以AT&T的DSp32C,TI的TMS320C30和TMS320C6xEVM,及MOTORALA的DSp56002EVM作为DSp的DLIA。这几种LIA根据实际需要和ADC与DAC转换速度的限制,工作频率在几Hz到几十kHz的低中频范围内,如果采用高速的ADC、DAC器件和高速的DSp处理器并采用并行分布式设计方法,工作在MHz的DLIA也是不难实现的。下面将着重介绍基于上述硬件结构的DLIA所需要的基本常用算法。

一般DLIA所共有的双通道正交相关算法,这种算法的基本思想源于正交矢量ALIA,但又有不同。参考信号的两个正交分量是根据内触发或外触发参考信号的频率和相位,通过DSp的内部查表方式而产生的。因此这两个正交信号不会因为内部触发信号和外部触发信号的形式(即正、余弦,方波或三角波参考信号)而改变。因此能消除由于参考信号是其它形式而造成的谐波分量的干扰。在内触发模式下,采用DAC和ADC的相同的采样频率,能使采样得到的被测信号和参考信号在相同采样点上的相位差恒定,从而消除了由于相位差不恒定而造成的干扰。相同采样时刻的采样数据分别与正交的两个参考信号在DSp中通过相乘运算就可以完成相关算法。为了降低由于采样和量化引入的各种相位噪声,还需要使采样频率设置为参考信号频率的整数倍,满足采样定理并要对被测信号进行抗混叠滤波。

3。基于pC的系统级模块化DLIA

基于pC的DLIA的硬件架构有两种模式:一种是用标准总线及标准机箱的硬件设计,如采用一种通用的VME-bus数据总线和3U,5VME板的6插槽标准机箱结构,这种结构的优点在于能将DLIA集成于一个复杂的数字系统中,同时也可以通过采用专用数据采集卡和数据处理卡来提高DLIA的性能;第二种是用通用数据总线的设备级硬件结构,这种结构主要是用于集成各种专用数字设备,如由Hp3325A信号源,Hp318计算机,KEITHLEY705扫描器和KEITHLEY194数字采集器或Hp3561A数字分析仪通过IEEE-488总线连接而成的DLIA系统。这两种都是开放式结构,易于系统升级,模块的高性能指标会使DLIA系统的性能更强,频带范围能从DC到几百MHz,甚至可以到GHz。这些优势使得ALIA望尘莫及。

关于数字锁相放大器,电子元器件资料就介绍完了,您有什么想法可以联系小编。