用门电路设计多谐振荡器最简单的办法是用奇数个门首尾相连。但这种振荡器精度低,振荡颇率也不能随心所欲的设计,它只是与奇数个门的延迟时间有关。阻容定时的多谐振荡器结构简单,定时精度高,振荡频率可以自由进行设计。

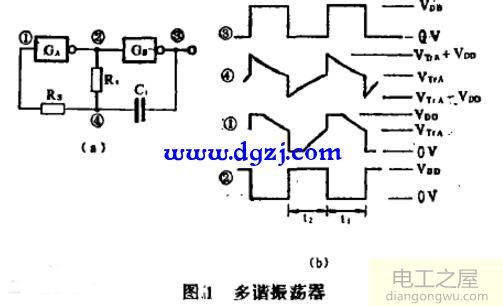

图1(a)为阻容定时的多谐振荡器电路图,GA、GB为CMOS反相器,R1、C1为定时元件,Rs为串联电阻。图1(b)是其各点的波形图,工作过程可用图2所示电路来说明。当接通电源后,⑧点电位上升,④点电位亦上升。当④点电位上升到GA门的Vtv电平时,GA被打开,②点跳变到低电平,③点上升到VDD电平。接着C1通过GA的“P”管,R1、C1、GA的“n”管放电,在放电的过程,④点电位按R1、C1的时间常数下降,当④点电位下降到VRA电平时,G门被关闭,②点跳变到接近VDD的电平,⑧点跳变到接近0V、④点电位跳变到(VRA一VDD)的电平上。接着C1通过G,的“p”管、C1、R1、GA的“n”管充电。就这样振荡下去。在③点和②点得到互补的输出波形。