今天小编要和大家分享的是FDSOI技术背景 FDSOI在移动领域的应用,接下来我将从FDSOI的技术背景,FDSOI在移动领域的应用,FDSOI的发展前景,这几个方面来介绍。

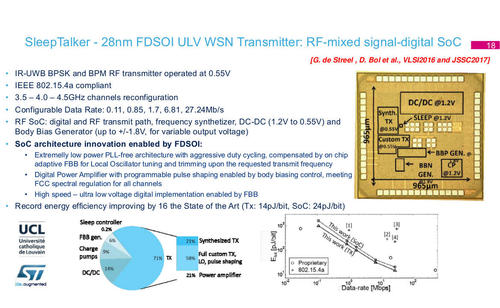

FDSOI技术即全耗尽型SOI技术,有些文献上也写成ETSOI即超薄型SOI,具有非常强的竞争力,适合20nm及更高级别制程的移动/消费电子产品使用。

FDSOI的技术背景

FD-SOI是下一代的主流技术是采用体硅技术制作的32/28nm制程平面型晶体管。

AMD,IBM以及其它部分厂商目前则在使用基于部分耗尽型SOI技术的平面型晶体管制造自己的处理器产品。相比之下,Intel公司过去则放弃了SOI的有关技术,称他们不需要这种技术。

对22/16nm级别制程而言,人们有多种晶体管结构可供选择,包括III-V族沟道技术,体硅技术,FinFET立体晶体管技术,FD-SOI全耗尽型平面晶体管技术,多栅立体晶体管技术等等,不过目前为止还没有哪种技术呈现出王者之象。

Intel公司负责制程技术的高管MarkBohr最近表示,Intel公司正在评价超薄SOI技术(即FD-SOI)。有些消息来源认为Intel在22或15nm节点制程可能会选择转向三栅极晶体管技术,不过Bohr拒绝就Intel的未来走向发表意见。

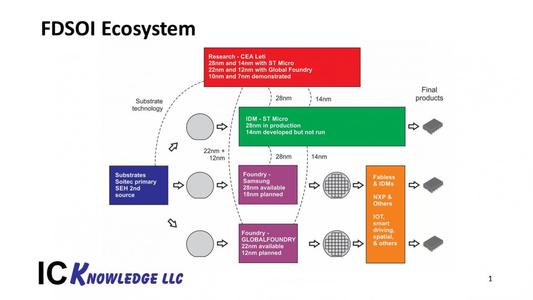

IBM公司半导体研发中心的副总裁Garypatton最近则表示FD-SOI是22nm制程节点的强势候选技术。不过部分芯片制造业的巨头如Globalfoundries,三星以及台积电则已经放出消息称他们在20nm节点会选择走体硅制程的道路,理由则是研发成本问题。

不过也有很多高性能应用中可能会需要使用FD-SOI技术。SOI指的是在IC的制造过程中采用硅+绝缘层+硅的硅基体结构方式,这种结构方式的优势是可以减小器件的寄生电容并改善器件的性能。

到FD-SOI,SOI中位于顶层的硅层厚度会减薄至5-20nm,这样器件工作时栅极下面沟道位置下方的耗尽层便可充满整个硅薄膜层,如此便可消除在pD-SOI中常见的浮体效应。

在部分耗尽型SOI结构中,SOI中顶层硅层的厚度为50-90nm,因此沟道下方的硅层中仅有部分被耗尽层占据,由此可导致电荷在耗尽层以下的电中性区域中累积,造成所谓的浮体效应。

FDSOI在移动领域的应用

FDSOI如何克服SOI的弱点

SOI令人头疼的一个问题是这种技术是否适合在移动设备市场使用,人们对SOI晶体管的所谓“历史效应”和尺寸可微缩空间保持怀疑的态度,因此多年来,SOI技术一直只在桌面型处理器和其它高性能应用中才有使用(编者按:SOI中热的不良导体BOX层(埋入式氧化物层)所导致的散热劣势应该也是其原因之一)。

如今,SOI联盟的成员终于将这项技术推进到了移动设备应用领域。在去年的SemicONWes商业会展仪式上,负责生产SOI基体的大腕级公司法国Soitec集团表示他们已经将自己的超薄埋入式时氧化物技术(UTBOX)拓展到了面向移动设备用的超薄SOI平台(即FD-SOI平台)。

Soitec生产的这些SOI硅晶圆顶层硅膜的厚度精度可以控制在±0.5nm之间,埋入式氧化物层的厚度则可达到10nm的水平,Soitec公司称这种晶圆可以满足其客户的要求。而且Soitec在法国和新加坡的工厂也已经具备量产这种晶圆的产能实力。

2008年,IBM公司属下的微电子集团推出了45nmSOI产品的代工服务项目,不过目前还不清楚IBM会不会继续提供基于FD-SOI技术的代工服务。

同时,Soitec抢在去年就宣布完成FD-SOI晶圆的生产准备也可能有点操之过急了。毕竟目前各大芯片厂商在下一代制程节点上是否会选择FD-SOI技术方面的表态还不够明确。也许芯片厂商还在为将FD-SOI技术应用到移动领域的有关设计问题感到担忧。

现在,SOI联盟的成员终于开始明确表态支持FD-SOI技术在移动领域的应用。SOI工业联盟的执行主席HoracioMendez表示:“FD-SOI是改变移动设备市场的伟大技术,这种技术可以提升移动设备在功耗,频率,可制造性以及成本费效等方面的性能。”他还表示FD-SOI技术在尺寸微缩方面具备优势,而且还可以与体硅技术兼容,同时还可以消除pD-SOI中的“历史效应”。

针对FD-SOI技术的初步测试显示,这种技术可以减小SRAM的工作电压100-150mV左右,如此便可减小存储器件的功耗40%左右,同时又可以保证SRAM工作的稳定性。

按照传统的理念,面向低功耗设备的新旧两代制程技术在性能方面的提升幅度一般在20-30%左右,而据SOI联盟发布的*估结果则显示使用FD-SOI技术制作的产品要比上一代pD-SOI技术提升80%的性能,超过了传统的性能增幅。

该联盟还表示,由于FD-SOI技术所使用的基体晶圆制作等级较高,因此后续的晶体管制造过程中,由于可以省去相当数量的掩模保护层制作过程,因此对于芯片制造商而言会相对简单,厂商今后进一步缩减晶体管尺寸时的制造成本费效比也会相对较低。

FDSOI的发展前景

体硅OS技术走到22nm之后,特征尺寸已很难继续微缩,急需革新技术来维持进一步发展。在候选技术之中,FDSOI(FullyDepletedSOI,全耗尽SOI)技术极具竞争力。对于FDSOI晶体管,硅薄膜自然地限定了源漏结深,同时也限定了源漏结耗尽区,从而可改善DIBL(DrainInducedBarrierLowering,漏致势垒降低)等短沟道效应,改善器件的亚阈特性,降低电路的静态功耗。此外,FDSOI晶体管无需沟道掺杂,可以避免RDF(RandomDopantsFluctuation,随机掺杂涨落)等效应,从而保持稳定的阈值电压,同时还可以避免因掺杂而引起的迁移率退化。

SOI晶圆制备技术的发展也为FDSOI投入应用提供了良好的支撑。为了使晶体管获得理想的性能,FDSOI晶圆的顶层硅膜和隐埋氧化层(BuriedOxide,BOX)须非常薄。目前市场上已出现相应的产品,可满足现阶段的应用需求。

SOI技术的发展环境也日益改善。自2007年SOI联盟(SOIConsortium)成立以来,越来越多的公司和机构开始关注SOI技术,并加入到推广SOI技术的队伍中。目前SOI联盟已有会员30个,包括科研机构、材料商、设备商、集成芯片制造商、芯片设计商、芯片代工商、供应商等,贯穿整个产业链。在这些厂商的努力下,产业对SOI的认识变得更为全面、准确和深入。

综上所述,FDSOI走向大规模应用的时机已经到来,如能成功地纵身一跃,将完成SOI技术发展史上最华丽的篇章。

关于FDSOI,电子元器件资料就介绍完了,您有什么想法可以联系小编。