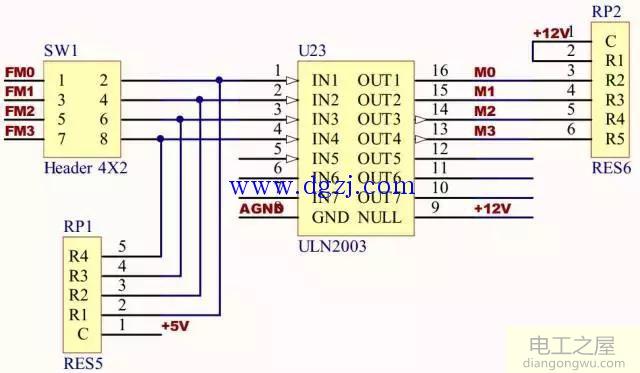

电机驱动电路原理如图2-1所示:

图2-1

图2-1中Header 4X2为4排2列插针,FM0~3为FPGA芯片I/O输出口,加入的插针给予一个可动的机制,在需要使用时才用跳线帽进行相连,提高I/O口的使用效率。RES5是五端口排阻,内部集成了4个等阻值且一端公共连接的电阻,PIN 1是公共端,PIN2~5为排阻的输出端,排阻原理图如图2-2所示:

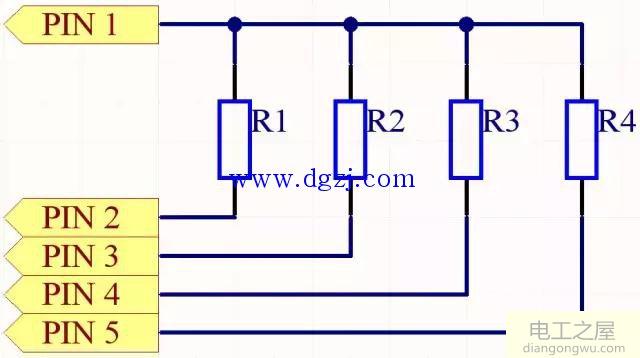

图2-2

该排阻公共端接电源,即上拉电阻形式,作用是增强FPGA芯片I/O口(以下简称I/O口)的驱动能力,实际上就是增加I/O输出高电平时输出电流的大小。当I/O输出高电平时,+5V电源经排阻与IN1~4相连,相当于为I/O提供一个额外的电流输出源,从而提高驱动能力。当I/O输出低电平时,可将I/O近似看做接地,而IN1~4因与I/O由导线直接相连,因此直接接受了I/O的低电平输出信号。此时,+5V电源经排阻R、I/O内部电路(电阻近似为零)后接地,因此该路的电流不能大于I/O的拉电流(Ii)最大值,有公式2-1:

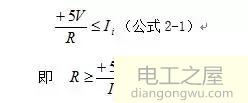

由公式2-2可以得出排阻的取值范围。

该上拉电阻除了提高驱动能力外,还有一个作用,就是进行电平转换。经查,ULN2003的接口逻辑为:5V-TTL, 5V-CMOS逻辑。而在3.3V供电的情况下,I/O口可以提供3.3V-LVTTL,3.3V-LVCMOS,3.3V-PCI和SSTL-3接口逻辑电平。因此,需要外接5V的上拉电阻将I/O电平规格变成5V电平逻辑。

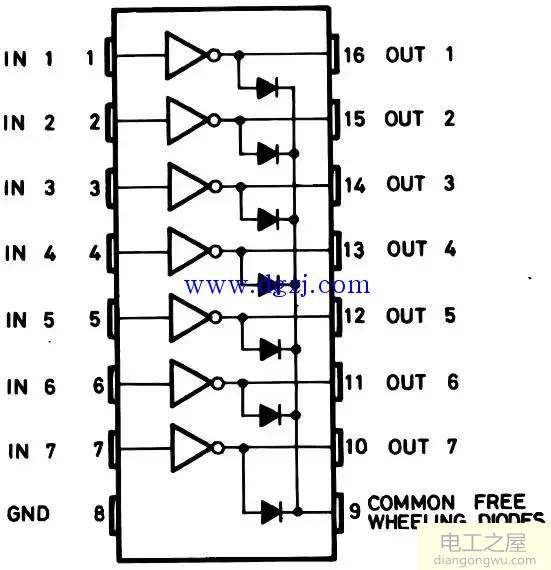

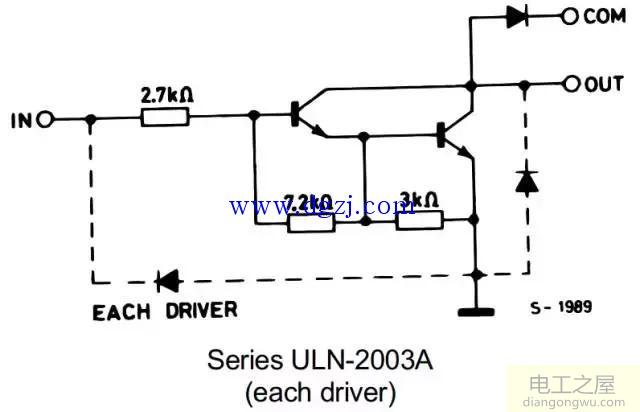

芯片ULN2003内部集成7组达林顿管,专门用于提高驱动电流,芯片引脚间逻辑如图2-3所示:

图2-3

图2-4

由于I/O电流远远不足以驱动电机,因此需要外接该芯片驱动电机,ULN2003内部集成的达林顿管电路如图2-4所示。达林顿管的形式具有将弱点信号转化成强电信号的特点,I/O电平逻辑从PIN IN输入,通过达林顿管控制PIN 9(COMMON)端输入的强电信号按照I/O信号规律变化。值得注意的是:ULN2003输出逻辑将与输入逻辑相反,编程时应该注意该特点。

RES6是六端口排阻,内部集成了5个等阻值且一端公共连接的电阻,PIN 1是公共端,PIN2~6为排阻的输出端,原理图与接法说明可参考上述图2-2,排阻取值范围计算参见公式2-2,此处不再赘述。值得注意的是:RES6的PIN 1与PIN 2相连,是因为多出了一个不使用的电阻,为了避免PIN 2悬空,因此将PIN 2与PIN 1(公共端)相连,即PIN 2对应的电阻被短路,从而既避免的悬空的引脚,又能使该电阻失效。