CMOS与非门芯片电路图及解剖过程

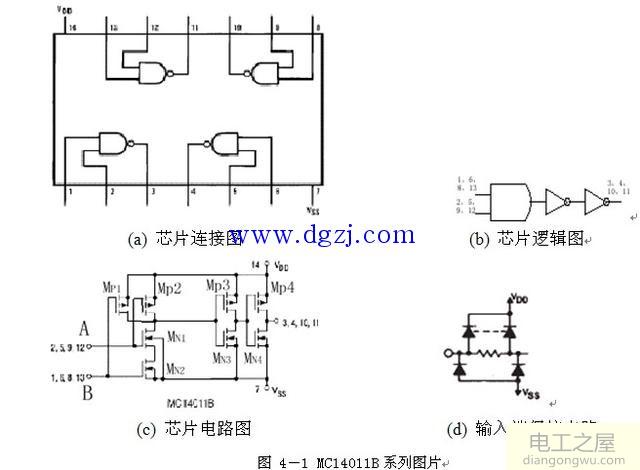

CD4011是一个四个两输入的与非门电路,他遵从标准的B系列输出驱动。该器件也包括了输出缓冲来提供高的增益以次提高传输特性。所有的输入端口都有二极管保护防止静态电流直接从VDD传输到VSS。

下图为a为CD4011的芯片连接图,b是它的逻辑电路,c是芯片内部的一个单元的电路图,d是输入栅保护电路:(从摩托罗拉公司网站下载编辑的)

MC14011B芯片解剖过程:

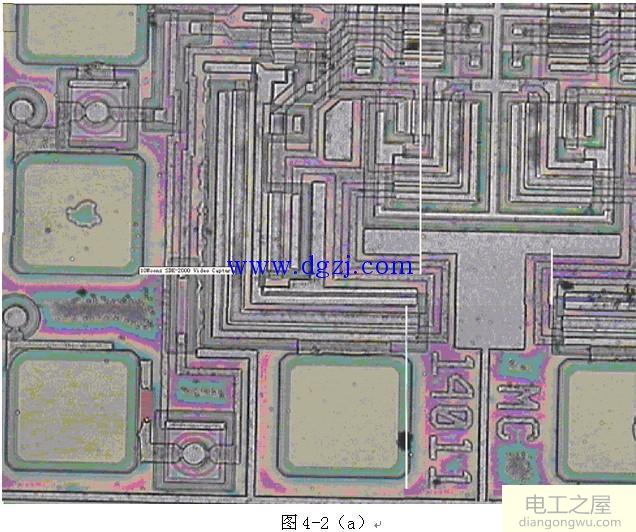

(1)拼图。由于本课题采用的是Motorola的CD4011芯片,其腐蚀难度比较大,所以备用两种照片,一种为有Al线的照片(已经除去氧化层),表面黑白分明,由于Al反光形成白色,所以看不到具体的管子;另一种为无Al线的照片,可以看到有源区、栅、扩散电阻等。

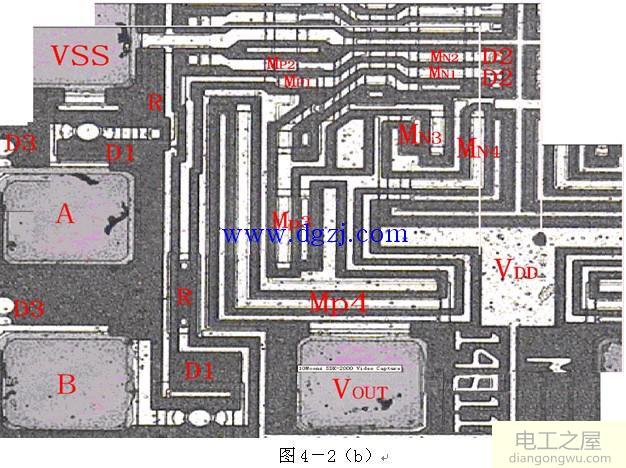

开始拼接前,在实验室用金相显微镜将芯片一个单元按一定的次序依次拍照,最后再拍一张全局图,图像虽不清晰,但可以作为后来拼图的依据。然后按顺序将图片排好,寻找相邻照片的共同点,用图像处理程序将其拼接起来。注意,由于照片可能有些偏差,不可能完全对上,因此只要重合最重要的部分,而且对准的时候从中心开始,这样可以保证中间的重叠比较好,外部可适当放低要求。本试验所拼版图照片如图4-2(a)、(b)

(2)标注。由2-3节提供的芯片管角图和电路图,寻找对应的电源Vdd和GND(Vss)的压焊块,找到后,确定输入输出压焊块,并注明功能,标号,如图4-2(b)。

(3)分块。从压焊块出发,经输入输出电路向内部走线,找到各输入端在内部的入口及各输出端在内部的出口,并做标记。由此将版图分成若干功能块,由输入信号确定各功能块的功能。

(4) 将各个功能块连在一起,画出总体逻辑图,提取各输出端逻辑表达式,进行时序逻辑分析。

(5)提取设计规则,量取各个管的宽长比标于电路图上,分析电路的特点。

(6)分析版图上的防止闭锁效应的措施。

(7)提取版图的布局布线,分析布局布线的整体特点。

(8)研究P阱和衬底接电位的问题。