d触发器构成异步二进制加法计数器

一、选用芯片74LS74,管脚图如下:

说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为

二、设计方案:

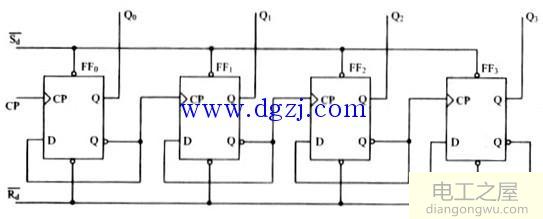

用触发器组成计数器。触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。如果把n个触发器串起来,就可以表示n位二进制数。对于十进制计数器,(https://www.dgzj.com/ 电工之家)它的10 个数码要求有10个状态,要用4位二进制数来构成。下图是由D触发器组成的4位异步二进制加法计数器。

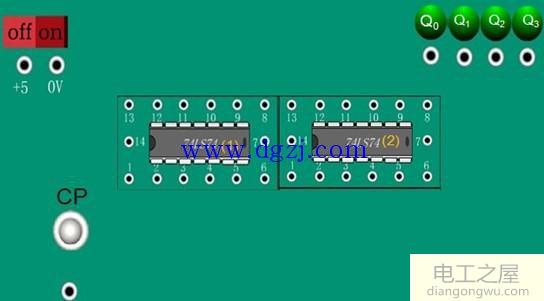

三、实验台:

四、布线:

1、将芯片(1)的引脚4、10连到一起,

2、将芯片(2)的引脚4、10连到一起,

3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,

4、将芯片(1)的引脚10连到+5V;

5、将芯片(1)的引脚1、13连到一起,

6、将芯片(2)的引脚1、13连到一起,

7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,

8、将芯片(1)的引脚13连到+5V;

9、将芯片(1)的引脚3接到时钟信号CP

10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚11

11、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚3

12、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚11

13、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q3

14、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:

接通电源on,默认输出 原始状态0000

每输入一个CP信号(单击CP), 的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111