1、 基准工作的基本原理

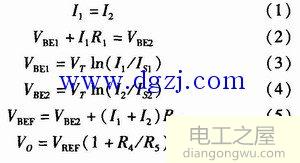

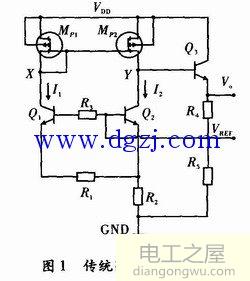

图1为典型的与温度无关的带隙基准电路架构图。它的原理就是利用三极管基极-发射极电压△VBE的负温度系数和两个三极管基极-发射极电压差值△VBE的正温度系数相抵消来产生零温度系数的基准电压。如图1所示,图中Mp1、Mp2为LDMOS管,VDD的大部分压降均落在Mp1、Mp2上,因此该电路可以承受较高的电源电压。若忽略三极管的基极电流,则有

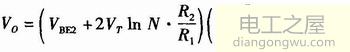

由式(1)~式(6)式可以得到

其中,N=IS1/IS2为QN1和QN2的发射极面积之比。VBE2的温度系数为-1.5 mV/℃,VT的温度系数为+0.086 mV/℃,所以选择适当的N值和R2/R1的比值,就可以得到零温度系数的输出电压。另外,调节R4和R5的比值,可以得到期望的基准电压,且不会改变已调整好的零温度系数特性。

2 、新颖的带隙基准电路

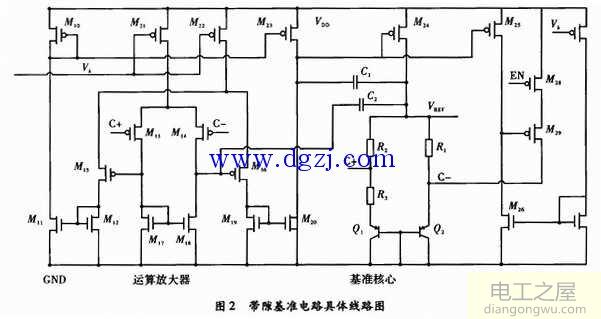

如图2即为所提出的基准电压电路。该电路由偏置、运算放大器、基准核心和基准启动4个部分构成。核心电路的原理如前文所述,下面对运放、启动作具体阐述。

该电路的运放如图2所示,运放的主要作用是保证△VBE的精准性。然而运放的失调是一个主要的误差源。假设输入端的失调电压为VOS,经过计算可以得到

这里的关键问题是失调电压被放大了(1+R2/R3)倍,在VREF中引入了误差。更重要的是VOS本身随温度变化,更增大了输出电压的温度系数。因此要尽量减少失调电压这里主要通过提高运放的增益和精确的版图设计来改进。如图2所示,基准中采用了多级差分结构的运放来提高其增益,增大负反馈的深度,减小失调。然而,运放级数的增多会增加电路的功耗,因此设计运放的偏置电流为与电源无关的较小量,使其工作在饱和区边缘,这也使得电路具有较宽的电源电压范围。

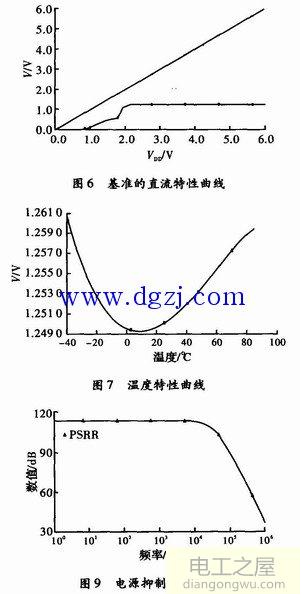

PSR是表征电源抑制能力的交流小信号参数,它的定义为输入电压的变化与输出基准电压的变化之比。在低频情况下,基准的PSR和运放的增益呈成正比。因此运放的环路增益越大,输出VREF对电源VDD变化的抑制性就越强。

而该电路的启动部分由M25,M26,M27,M28,M29和M30组成,Vb由偏置部分产生,EN为使能信号,正常工作时为低电平。当EN为低时,且Vb达到一定电平时,M30导通,M30,M27支路产生电流,使M26和M27的栅电位升高,M26便将M29的栅电位拉低,M28,M29支路产生电流,使基准部分开始工作。设计M25的宽长比远大于M26的宽长比,使得基准正常工作后M28的栅电位为高,关断M28,M29支路,启动部分与基准脱离。

3 、仿真结果

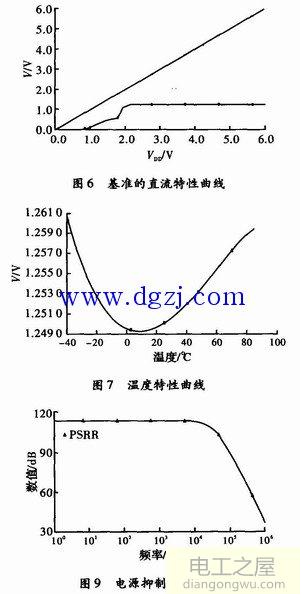

对设计的带隙基准电路进行了性能指标的仿真。从图6中基准的直流特性可见,电源电压在1.5~6V之间变化时,基准输出仍保持良好的稳定性;图7为基准的温度特性曲线,当温度从-40~100℃变化时,基准电压的变化仅为2.2 mV,温度系数为13.7×10-6/℃,显示了低温漂的特性;图8是基准环路稳定性的仿真曲线,基准的环路增益为110 dB,相位裕度为67°;图9是基准的电源抑制特性的仿真波形,低频时PSR为-117 dB.仿真结果都满足性能指标。