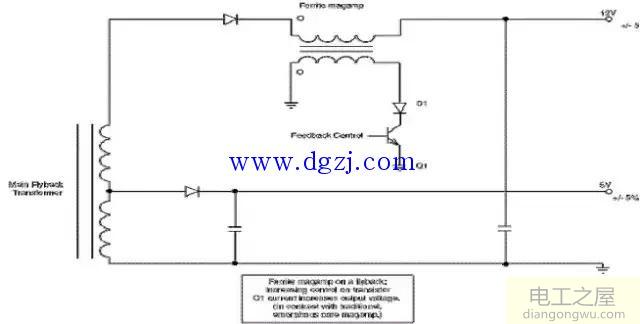

反激式电源中的铁氧体磁放大器对于两个输出端都提供实际功率( 5 V 2 A 和 12 V 3 A ,两者都可实现± 5% 调节)的双路输出反激式电源来说,当电压达到 12 V 时会进入零负载状态,而无法在 5% 限度内进行调节。线性稳压器是一个可实行的解决方案,但由于价格昂贵且会降低效率,仍不是理想的解决方案。我们建议的解决方案是在 12 V 输出端使用一个磁放大器,即便是反激式拓扑结构也可使用。

为了降低成本,建议使用铁氧体磁放大器。然而,铁氧体磁放大器的控制电路与传统的矩形磁滞回线材料(高磁导率材料)的控制电路有所不用。铁氧体的控制电路( D1 和 Q1 )可吸收电流以便维持输出端供电。该电路已经过全面测试。变压器绕组设计为 5 V 和 13 V 输出。

该电路在实现 12 V 输出± 5% 调节的同时,甚至还可以达到低于 1 W 的输入功率( 5 V 300 mW 和 12 V 零负载)。

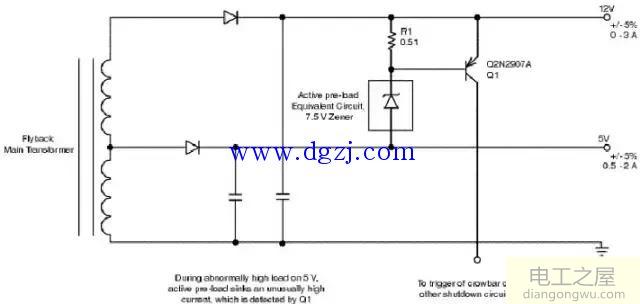

考虑一下 5 V 2 A 和 12 V 3 A 反激式电源。该电源的关键规范之一便是当 12 V 输出端达到空载或负载极轻时,对 5 V 输出端提供过功率保护 (OPP) 。这两个输出端都提出了± 5% 的电压调节要求。

对于通常的解决方案来说,使用检测电阻会降低交叉稳压性能,并且保险丝的价格也不菲。

而现在已经有了用于过压保护 (OVP) 的消弧电路。该电路能够同时满足 OPP 和稳压要求,使用部分消弧电路即可实现该功能。

从图 1 可以看出, R1 和 VR1 形成了一个 12 V 输出端有源假负载,这样可以在 12 V 输出端轻载时实现 12 V 电压调节。在 5 V 输出端处于过载情况下时, 5 V 输出端上的电压将会下降。假负载会吸收大量电流。 R1 上的电压下降可用来检测这一大量电流。 Q1 导通并触发 OPP 电路。

在线电压 AC 到低压 DC 的开关电源产品领域中,反激式是目前最流行的拓扑结构。这其中的一个主要原因是其独有的成本效益,只需向变压器次级添加额外的绕组即可提供多路输出电压。

通常,反馈来自对输出容差有最严格要求的输出端。然后,该输出端会定义所有其它次级绕组的每伏圈数。由于漏感效应的存在,输出端不能始终获得所需的输出电压交叉稳压,特别是在给定输出端因其它输出端满载而可能无负载或负载极轻的情况下更是如此。

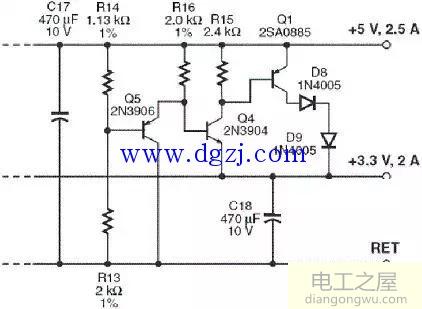

可以使用后级稳压器或假负载来防止输出端电压在此类情况下升高。然而,由于后级稳压器或假负载会造成成本增加和效率降低,因而它们缺乏足够的吸引力,特别是在近年来对多种消费类应用中的空载和 / 或待机输入功耗的法规要求越来越严格的情况下,这一设计开始受到冷落。图 1 中所示的有源并联稳压器不仅可以解决稳压问题,还能够最大限度地降低成本和效率影响。

图 1 - 用于多路输出反激式转换器的有源并联稳压器

该电路的工作方式如下:两个输出端都处于稳压范围时,电阻分压器 R14 和 R13 会偏置三极管 Q5 ,进而使 Q4 和 Q1 保持在关断状态。在这样的工作条件下,流经 Q5 的电流便充当 5 V 输出端很小的假负载。

5 V 输出端与 3.3 V 输出端的标准差异为 1.7 V 。当负载要求从 3.3 V 输出端获得额外的电流,而从 5 V 输出端输出的负载电流并未等量增加时,其输出电压与 3.3 V 输出端的电压相比将会升高。由于电压差异约超过 100 mV , Q5 将偏置截止,从而导通 Q4 和 Q1 并允许电流从 5 V 输出端流到 3.3 V 输出端。该电流将降低 5 V 输出端的电压,进而缩小两个输出端之间的电压差异。

Q1 中的电流量由两个输出端的电压差异决定。因此,该电路可以使两个输出端均保持稳压,而不受其负载的影响,即使在 3.3 V 输出端满载而 5 V 输出端无负载这样最差的情况下,仍能保持稳压。设计中的 Q5 和 Q4 可以提供温度补偿,这是由于每个三极管中的 VBE 温度变化都可以彼此抵消。使用三相交流电进行工作的工业设备常常需要一个可以为模拟和数字电路提供稳定低压直流电的辅助电源级。此类应用的范例包括工业传动器、UPS 系统和能量计。

此类电源的规格比现成的标准开关所需的规格要严格得多。不仅这些应用中的输入电压更高,而且为工业环境中的三相应用所设计的设备还必须容许非常宽的波动—包括跌落时间延长、电涌以及一个或多个相的偶然丢失。而且,此类辅助电源的指定输入电压范围可以达到 57 VAC 至 580 VAC 之宽。

设计如此宽范围的开关电源可以说是一大挑战,主要在于高压 MOSFET 的成本较高以及传统的 PWM 控制环路的动态范围的限制。 StackFET 技术允许组合使用不太昂贵的、额定电压为 600V 的低压 MOSFET 和 Power Integrations 提供的集成电源控制器,这样便可设计出简单便宜并能够在宽输入电压范围内工作的开关电源。

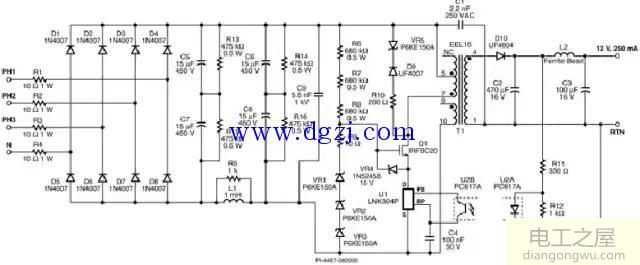

图 1 – 采用 StackFET 技术的三相输入 3W 开关电源

该电路的工作方式如下:电路的输入端电流可以来自三相三线或四线系统,甚至来自单相系统。三相整流器由二极管 D1-D8 构成。电阻 R1-R4 可以提供浪涌电流限制。如果使用可熔电阻,这些电阻便可在故障期间安全断开,无需单独配备保险丝。 pi 滤波器由 C5 、 C6 、 C7 、 C8 和 L1 构成,可以过滤整流直流电压。

电阻 R13 和 R15 用于平衡输入滤波电容之间的电压。

当集成开关 (U1) 内的 MOSFET 导通时, Q1 的源端将被拉低, R6 、 R7 和 R8 将提供栅极电流,并且 VR1 到 VR3 的结电容将导通 Q1 。齐纳二极管 VR4 用于限制施加给 Q1 的栅极源电压。当 U1 内的 MOSFET 关断时, U1 的最大化漏极电压将被一个由 VR1 、 VR2 和 VR3 构成的 450 V 箝位网络箝位。这会将 U1 的漏极电压限制到接近 450 V 。与 Q1 相连的绕组结束时的任何额外电压都会被施加给 Q1 。这种设计可以有效地分配 Q1 和 U1 之间的整流输入直流电压和反激式电压总量。电阻 R9 用于限制开关切换期间的高频振荡,由于反激间隔期间存在漏感,箝位网络 VR5 、 D9 和 R10 则用于限制初级上的峰值电压。

输出整流由 D1 提供。 C2 为输出滤波器。 L2 和 C3 构成次级滤波器,以减小输出端的开关纹波。

当输出电压超过光耦二极管和 VR6 的总压降时, VR6 将导通。输出电压的变化会导致流经 U2 内的光耦二极管的电流发生变化,进而改变流经 U2B 内的晶体管的电流。当此电流超出 U1 的 FB 引脚阈值电流时,将抑制下一个周期。输出稳压可以通过控制使能及抑制周期的数量来实现。一旦开关周期被开启,该周期便会在电流上升到 U1 的内部电流限制时结束。 R11 用于限制瞬态负载时流经光耦器的电流,以及调整反馈环路的增益。电阻 R12 用于偏置齐纳二极管 VR6 。

IC U1 (LNK 304) 具有内置功能,因此可根据反馈信号消失、输出端短路以及过载对该电路提供保护。由于 U1 直接由其漏极引脚供电,因此不需要在变压器上添加额外的偏置绕组。C4 用于提供内部电源去耦。(二极管 D8 和 D9 不是必需的器件,但可用于降低 Q1 中的功率耗散,从而无需在设计添加散热片。

该电路只对两个电压之间的相对差异作出反应,在满载和轻负载条件下基本不起作用。由于并联稳压器是从 5 V 输出端连接到 3.3 V 输出端,因此与接地的并联稳压器相比,该电路的有源耗散可以降低 66% 。其结果是在满载时保持高效率,从轻负载到无负载的功耗保持较低水平。

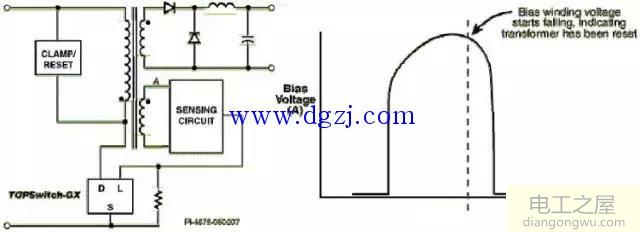

该电路能确保变压器在每个周期进行复位,因此可大大简化使用 TopSwitch-GX 设计正激式转换器的过程。

检测电路与正激式转换器偏置绕组配合使用可以检测关断期间的电压波形。当此间电压较高时,信号会应用于 TopSwitch-GX L 引脚,使其断开与 S 引脚的连接,从而抑制内部 MOSFET 开始另一个导通周期。当偏置绕组上的电压信号开始衰弱时,即表示变压器已经复位, L 引脚与 S 引脚相连,开关已开启选择好的整流二极管可以简化 AC/DC 转换器中的 EMI 滤波器电路并降低其成本该电路可以简化 AC/DC 转换器中的 EMI 滤波器电路并降低其成本。

要使 AC/DC 电源符合 EMI 标准,就需要使用大量的 EMI 滤波器器件,例如 X 电容和 Y 电容。

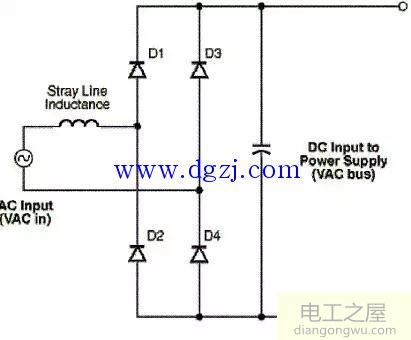

AC/DC 电源的标准输入电路都包括一个桥式整流器,用于对输入电压进行整流(通常为 50-60Hz )。由于这是低频 AC 输入电压,因此可以使用如 1N400X 系列二极管等标准二极管,另一个原因是这些二极管的价格是最便宜的。

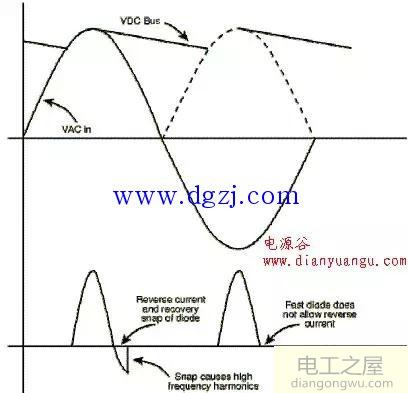

这些滤波器器件用于降低电源产生的 EMI ,以便符合已发布的 EMI 限制。然而,由于用来记录 EMI 的测量只在 150 kHz 时才开始,而 AC 线电压频率只有 50 或 60 Hz ,因此桥式整流器中使用的标准二极管(参见图 1 )的反向恢复时间较长,且通常与 EMI 产生没有直接关系。

然而,过去的输入滤波电路中有时会包括一些与桥式整流器并联的电容,用来抑制低频输入电压整流所造成的任何高频波形。

如果在桥式整流器中使用快速恢复二极管,就无需使用这些电容了。当这些二极管之间的电压开始反向时,它们的恢复速度非常快(参见图 2 )。这样通过降低随后的高频关断急变以及 EMI ,可以降低 AC 输入线中的杂散线路电感激励。由于 2 个二极管可以在每半个周期中实现导通,因此 4 个二极管中只需要 2 个是快速恢复类型即可。同样,在每半个周期进行导通的两个二极管中,只需要其中一个二极管具有快速恢复特性即可。

图 1. 在 AC 输入端使用桥式整流器的 SMPS 的典型输入级

图 2. 输入电压和电流波形显示了反向恢复结束时的二极管急变。

对 Power Integrations 的多数产品而言,数据手册中限制的用于确保正常启动和起作用的最小漏极电压为 50 V 。但是,如果通过外部电源向旁路引脚馈电,则芯片可接收外部供电,且即使在较低的输入电压下也可启动和工作。

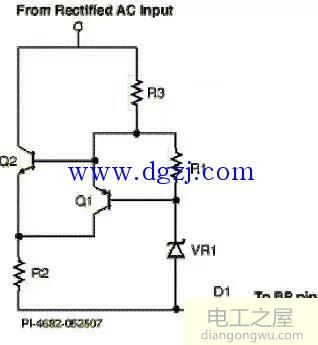

图 1. 功率控制器的浮动恒流源电路

图 1 所示的启动电路为浮动恒流源,它为整个输入电压范围内的 TinySwitch-III 的旁路 (BP) 引脚提供大约 600 μ A 的恒流。

恒流值由 R2 和 VR1 确定:

该电路源自基本的单晶体管电流源。该电路采用了一个齐纳二极管,为 Q2 (NPN) 的基极引出端设置参考电压,并以此对流经电阻 R2 的固定电压进行编程,从而设置恒流值。然而,鉴于输入电源范围的异常宽广性,参考齐纳二极管的偏置电流在很大范 s 围内会有所差异。这将导致功率耗散增加及编程的恒流发生偏移。

要克服上述难题,需要由其他的电流源(由 Q1 (PNP) 与 R1 形成)提供偏置电流。将等同于 VBE 的恒压强加于 R1 ,这样可为整个工作范围内的参考齐纳二极管提供偏置电流补偿。

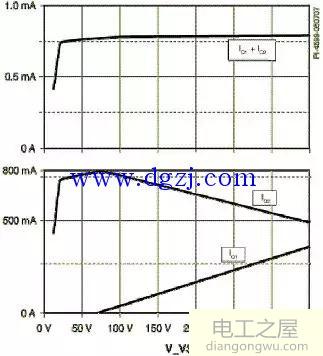

晶体管 Q2 以较低输入电压提供恒流,而 Q1 则以较高的输入电压提供恒流。图 2 显示了电流流经 Q1 和 Q2 时的模拟结果。输入电压达到大约 50 VDC 时, Q2 将提供恒流。输入电压达到 50 VDC 及以上时,经过 Q2 的电流将减弱,而经过 Q1 的电流则呈线性增加。输入电压达到最大值 375 VDC 时,则主要由 Q1 提供恒流。

R3 用于限制整个电路在输入电压最大时的输入电流。

图 2. 超过输入电压时的晶体管电流与总的旁路 (BP) 引脚电流

非线性电流由于齐纳二极管 VR1 的非线性活动而上升。输入电压大约为 60 VDC 时,齐纳二极管开始有电压为满足严格的待机功耗规范要求,一些多路输出电源被设计为在待机信号为活动状态时断开输出连接。通常情况下,通过关闭串联旁路双极晶体管 (BJT) 或 MOSFET 即可实现上述目的。

对于低电流输出,如果在设计电源变压器时充分考虑到晶体管的额外压降情况,则 BJT 可成为 MOSFET 的合适替代品,且成本更为低廉。

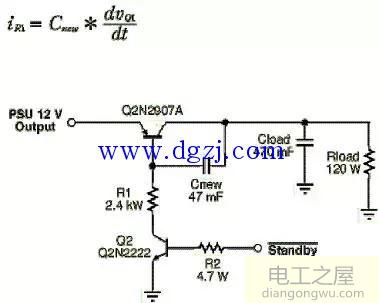

图 1 所示为简单的 BJT 串联旁路开关,电压为 12 V ,输出电流强度为 100 mA ,并带有一超大电容 (CLOAD) 。晶体管 Q1 为串联旁路元件,由 Q2 根据待机信号的状态来控制其开关。电阻 R1 的值是额定的,这样可确保 Q1 有足够的基值电流在最小 Beta 和最大的输出电流下以饱和的状态工作。 PI 建议额外添加一个电容器 (Cnew) ,用以调节导通时的瞬态电流。如果不添加 Cnew , Q1 在导通后即迅速进入电容性负载,并因而产生较大的电流尖峰。为调节该瞬态尖峰,需要增加 Q1 的容量,这便导致了成本的增加。

用作 Q1 额外“密勒电容”的 Cnew 可以消除电流尖峰。该额外电容可限制 Q1 集电极的 dv/dt 值。 dv/dt 值越小,流入 Cload 的充电电流就越少。为 Cnew 指定电容值,使得 Q1 的理想输出 dv/dt 值与 Cnew 值相乘等于流入 R1 的电流