随着采用大型BGA封装的可编程器件的应用不断普及,以及高密度互连(HDI)、时序关键的差分对信令的广泛应用,现在再采用这样一种相互隔离的PCB设计方式将带来灾难性后果,而并行开发流程允许多个开发过程同步进行,有助于确保设计成功,避免延误、额外开销以及返工。本文总结了并行 PCB设计各个阶段的关键准则。

PCB设计的第一步是在概念阶段。这时,电路设计工程师应该与PCB设计工程师一起进行技术评估。这个评估应考虑这么一些问题:

1. 采用哪些器件?

2. 器件选用哪种封装?管脚数多少?管脚配置怎样?

3. 基于成本和性能的权衡,采用几层PCB?

4. 时钟频率和信令速度等参数的目标值是什么?

此外,设计工程师还应考虑总线架构、是采用并行还是串行连接等因素,以及阻抗匹配策略。阻抗不匹配时会出现反射、振铃及其它不期望的干扰。

协同工作

PCB设计的这些考虑提出了成功PCB设计中的一个关键问题是沟通,因为PCB设计不再是一个人的工作,而是不同组的工程师之间的团队合作。沟通这一主旨贯穿整个PCB设计流程的始终,电路设计团队必须清楚地就其设计意图与PCB设计团队进行沟通,他们还必须在清楚了解其PCB设计工具能干什么、不能做什么的前提下参与到该过程中。

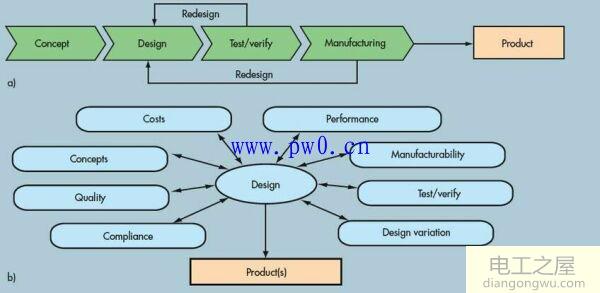

随着PCB布线的复杂性日益增加,信号速率日益提高,协同的PCB设计方式可比传统的串行流程得到更好效果(图1)。将对元件的研究和选择与整个设计流程的其它部分隔离开,以及将原理图输入、仿真与布局布线阶段也独立出来一直是常用手法。因此,设计工程师最好选择便于分享数据的工具和流程,这是在分布在不同地方的设计团队能利用并行工作的好处并缩短整个设计周期的唯一途径。

并行PCB设计的关键准则

图:(a) 传统PCB串行开发流程的设计周期长,信息共享有限,而成本持续上升;(b) 并行开发流程允许多个开发程同步进行,有助于确保设计成功,避免延误、额外开销以及返工。

设计创建

在设计创建阶段,工程师将最终确定好器件并为其生成各种库,这样反过来又加快了原理图输入。在该阶段,设计工程师评估和选择构造模块,并可以登陆制造商的网站搜索数据表和规范。完成这项工作的一个更好方法,是直接在原理图输入过程中选择器件。通过以这种方式来实现原理图输入,这个流程可被用作为一种试验方法。

在原理图输入过程中,设计工程师能迅速添加、删减或变更器件(甚至整个设计结构)的能力很重要。例如,为手机开发高频滤波器的设计工程师应在原理图输入时,通过对不同容抗和感抗值进行试验来设定通带及其它滤波器参数。

在创建原理图时,PCB设计工具也在后台为该电路生成一个网络表。网络表描述了电路的器件如何连接以及后续放置和布线工具如何将其用于PCB布局布线的信息。

此时,设计工程师将为诸如FPGA或其它可编程器件等所谓的“大元件”创立符号和物理管脚布局布线图。也是在这个时候,设计约束被捕获,这是一个需要审慎思考的关键步骤,特别是对后续流程而言。

对于目前的PCB设计来说,最好一切都按规矩办。过去是受到制造问题的制约,而现在当工程师努力减小PCB的体积且仍使其具有可制造性时,一切都要受到复杂约束的限制。虽然设计需求也许会导致大量约束,但不让设计被过分约束也很重要。与简单地用约束设计相比,更多地借鉴仿真和分析是更明智的方法。

在设计创建过程中,工程师需留意也许会在后续流程中出现的信号完整性问题。最好在设计输入阶段及PCB布局布线阶段就将信号完整性问题考虑进去,当然设计流程必须支持这种方式,因为无法在设计输入阶段解阻抗失配问题。

仿真是关键

电路一旦设计完成并绘制好原理图后,接着就该进行功能验证,它通常采用仿真工具完成。仿真的目的不是取代物理原型生成,而为了避免反复生成原型,因为仿真使设计工程师能发现一般要等到原型生成才能发现的设计缺陷。

在仿真过程中,可以尝试各种设计拓扑,并用不同厂商的器件进行替代,来检验它们对电路性能的影响。但在仿真时,伴随模型的可用性及有效性的问题层出不穷。目前所有常用的PCB设计工具包都带有昂贵的模型库,但可能不止一次会出现某个特定器件不在库内的情况。但器件供应商一般会通过在其网站上推出Spice模型来解决此问题,因此通过器件供应商网站查找它们是个好主意。

迂回布线的限制

但基于Spice的仿真也存在局限性,它能生成理想化从而不一定代表真实条件的仿真信号。真实信号可能有改变真实性的噪声和相移。

美国国家仪器公司(NI)的PCB设计流程包括虚拟仪器,可将该仪器与NI的许多PXI仪器一起使用,以生成保留随带的非线性成分的真实信号。这些信号能以固有的文件格式来捕获,以用在验证电路行为的Spice仿真上。另外,虚拟原型可提供对器件选择的反馈。

系统级的仿真也很关键,它不仅仅是对一个通过PCB的信号实施建模,还必须检查信号在器件内甚或通过多个板卡时都有什么变化。数Gb的信令速率是使情况更复杂的另一个因素。串行总线架构比并行总线架构更受青睐,这就要求PCB设计工程师对损耗、耦合传输线及详尽的过孔模型实施仿真。

物理实现

当通过仿真剔除性能问题后,下一步是对电路进行布局布线以生成物理原型。布局布线要确保电路性能满足设计规范要求,并保证板卡外形匹配设计形态参数。这时与机械工程师一起合作将非常必要。

在布局布线阶段,由原理图定义的器件间的互连可由任一家EDA供应商提供的布局布线和布线工具实现。所有这些工具都将提供一定程度的自动布局布线功能,但它是一把双刃剑。设计工程师需要判断何时进行手工布线,何时采用自动布线。如果要放置一个关键元件,或者必须将一个连接器放在PCB边缘上,就不要采用自动布局布线功能。

欣慰的是,在进行布局布线时,可以对信号完整性问题做些前瞻性考虑。这是个必须认真对待的阶段。一般的经验是,如果信号到达目的地所用的时间超过转换时间的1/3,则在该路径上可能存在信号完整性问题。

设计约束

PCB布局布线存在许多挑战,其中最主要挑战是确保满足约束条件。这些约束被用来解决信号完整性问题、可制造性问题、电磁干扰、热效应或上述这些问题的组合。

除设计约束外,许多与目前特定器件技术相关的因素使PCB布局布线更加复杂,例如板载芯片(COB)等先进半导体封装技术可令布线变得极其棘手。目前的高密度封装可以容下2,000多个管脚,管脚间距不到0.65mm。这种封装将给管理I/O和信号速度带来很大困难,对这种封装进行迂回布线(Escape Routing)也是一个高技巧工作。

对可编程逻辑器件进行PCB布局布线是另一个挑战。一些高端PCB设计工具包(比如Altium和Mentor Graphics公司提供的PCB设计工具包)能与FPGA供应商的设计工具紧密链接,并可用来完成FPGA和PCB本身的集成设计。

以前,大型FPGA的管脚配置一般由FPGA设计工程师完成,但在进行配设时并没对PCB布局布线有太多考虑。人们现在意识到,带可编程I/O的FPGA是走线进或出的源头,改变FPGA以迎合PCB布局布线比改变PCB来匹配FPGA的I/O设置要容易地多。

最后检查

在将PCB版图拿去制造前的最后步骤是最终检查。必须检查信号完整性和时序以确保信号能及时到达目的地并具有充分的品质保证。设计约束冲突将在此时表露出来,对此要进行权衡。

在该阶段,最大挑战之一是尽量将这些设计流程的最后验证步骤提前,具有更好的约束是实现这种要求的一个关键。若在创建设计过程中,在确定约束的同时还可进行分析,则改善约束条件的质量。

PCB设计最后必须生成制造数据,包括全部与生产、组装及测试相关的文档。在整个设计过程中,设计团队成员与制造厂家之间必须都有充分沟通,以了解制造商的技术能力和限制。另外,必须对制造数据进行验证以使设计工程师有最后机会发现错误。

备注:本文采用了Zuken公司的高级应用工程师Ed Duranty、美国国家仪器公司(NI)的产品营销工程师Bhavesh Mistry、Mentor Graphics公司的业务拓展总监David Wiens、Altium公司的产品知识总监Phil Loughhead和产品营销经理Rob Irwin的部分观点。