可以分为两部分:(1)设计出一个输出10M~100MHZ方波信号;(2)将方波信号幅值增大至1000V。

设计出一个输出10M~100MHZ方波信号

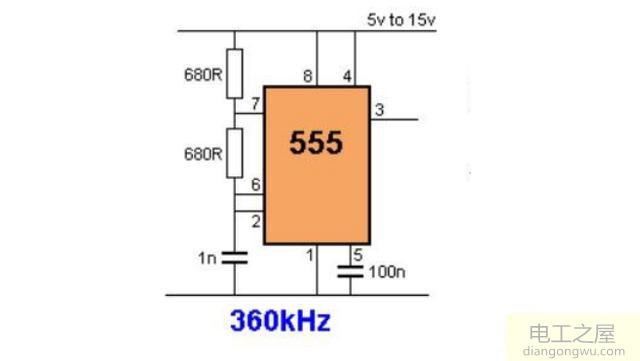

频率为10M~100MHZ的方波信号,那么它的周期为T=1/f,则周期在10ns~100ns之间。可以看出频率是非常高的,属于高频的范畴,高频电路设计还是相当有难度的,很多器件在高频电路当中无法使用。比如555定时器,这是输出方波最常用的芯片,设计信号发生器时,很多人会想起555定时器。

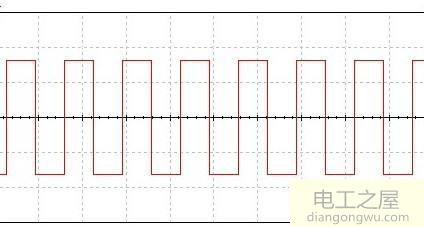

但是对于输出10M~100MHZ方波信号,555定时器是根本实现不了的,555定时器的最大输出频率大约为360KHZ左右,大于该频率输出波形会不规则或者出现故障。

10M~100MHZ的超高频方波信号虽然在设计上有点难,还是可以实现的,比如可以使用FPGA实现,FPGA的处理速度比DSP高多了,FPGA的时钟最高也就800M左右,使用FPGA进行分频,可以实现输出输出10M~100MHZ的方波信号(幅值3.3V)。

将方波信号幅值增大至1000V

若是低频的方波信号,想要将其电压幅值增大至1000V,还是比较容易实现的,可是使用耐压大于1000V的晶体管或场效应管实现,但是想要实现将10M~100MHZ的超高频方波信号的幅值扩大至1000V,根本没有满足这样条件的三极管或场效应管,有高频的晶体管最高频率可达1GHZ以上,但是其耐压值一般几十伏,根本达不到1000V。

频率为10M~100MHZ的方波,其周期为10ns~100ns之间,在这个时间内要实现峰值为1000V的一个周期的方波,也就是说这个时间内要实现从0V升到1000V,然后从1000V降到0V的过程,可能吗?个人认为是完全不可能的。