用verilog写移位寄存器

线性反馈移位寄存器 = 移位寄存器 + 组合逻辑反馈

●用处:产生伪随机序列、数据压缩、计数器、数据编码解码等等

●好处:具有速度和面积优势

●特点:

★产生伪随机序列的最大长度:2^n-1;

●种类:

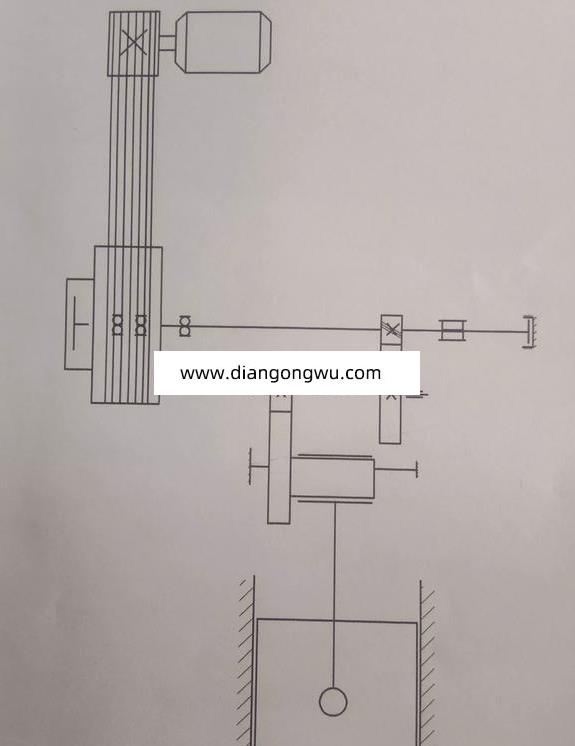

one_to_many:

many_to_one:

●“最大”的线性反馈移位寄存器

★最大是指能产生的伪随机序列长度最长

★一个D触发器叫做移位寄存器中的一个比特,D触发器的数目称为移位寄存器的比特数

★“最大”的移位寄存器表(one_to_many):

如下图所示的移位寄存器,如果进入状态0000(即四个D触发器的值都是0),那么就永远出不来了

如下图所示的移位寄存器,如果进入状态0000(即四个D触发器的值都是0),那么就永远出不来了

预防办法:

(1)想办法给寄存器置位到某个允许的状态

(2)用额外的电路让寄存器能够从禁止状态自动进入允许状态

以8个比特的线性反馈移位寄存器为例:

参照“最大”的移位寄存器表,先做一个2^n-1状态的移位寄存器:

其实,只要寄存器状态不是00000000,寄存器就会正常工作,如果寄存器的状态是00000000,那么寄存器就会永远被困在状态00000000中。

我们要做的工作是:

把00000000也变成正常工作状态。

这需要:

(1)我们能从某个正常状态转到00000000,

(2)我们能从00000000转到另一个正常工作状态

(3)加入00000000尽量不影响其他状态之间的转移。

首先看(2)和(3),如果我们能实现下图所示的电路,就能满足(2)和(3)。

此时,00000000的下一个状态是10111000

正好是图1所示电路中00000001的下一个状态。

所以我们让00000001转到00000000

下图所示电路就能满足要求:

综上:同时满足(1)、(2)、(3)的电路如下图所示:

其对应的many_to_one实现是:

●难点:

★要把n当成参数传入LFSR设计模块中

★要能综合

★要使用尽量少的资源,尽量不使用rom

●设计参照:

●代码分析:

小结:这段代码最经典的地方就在第一个always(即always @(reset))里面,这里写了这么多,看似会被存在一个rom中,其实,经过综合工具优化后,TapsArray根本就不会出现在电路里,既实现了通用性,又不会带来额外电路开销。看来,综合工具也是可以被设计者利用的,了解综合工具的脾性,可以提高我们的设计质量。

●模块调用:

veriloghdl助一个8位移位寄存器。。不知道怎么回事,总是没对

module yiweijicun(in,out,clk,rst);

input [7:0] in;

input clk,rst;

output [7:0] out;

reg [7:0] out;

reg [7:0] temp;

always @(posedge clk)

begin

if (!rst)

out=0;

else

begin if(load)

temp=in;

else begin

out=(out<<1);

out[0]=temp[7];

end

end

end

endmodule

verilog移位寄存器跟赋值关系教

【1】你的理解是对的!你在一个always里面用两次非阻塞赋值,在一个时钟边沿处理同一个变量hx,就成了这样。

【2】你按这个思路想:在hx被赋值以后,先保证hx不再被重复赋值冲掉数据,然后再移位操作。例如,赋值以后加一个使能信号,在使能信号下移位

【3】欢迎采纳!欢迎提问!

用VerilogHDL编程设计8位左右移移位寄存器电路。

module Verilog1(clk,ldn,k,d,q);

input clk,ldn,k;

input [7:0] d;

output [7:0] q;

reg[7:0] d_reg,q_reg;

always@(negedge ldn)

if(!ldn)

d_reg <= d;

always@(posedge clk )

begin

if(k)

begin//right

q_reg[7:0] <= {1'b00,d_reg[7:1]};

end

else q_reg[7:0] <= {d_reg[6:0],1'b0};

end

assign q = q_reg;

endmodule

移位寄存器verilog代码

//这个程序串行输入,并行8位输出

module yiwei(in,clk,en,clr,set,out);

input en,set,clk,clr;

input in;

output [7:0] out;

reg [7:0] out;

always@(posedge clk or negedge clr)

begin

if(!clr)//异步清零

begin

out<=0;

end

else

begin

if(en & set) out<=8'b11111111;//置位

else if(en)//使能

begin

out<=out<<1;

out[0]<=in;

end

else

out<=out;

end

end

endmodule

移位寄存器verilog代码、verilog移位寄存器,就介绍到这里啦!感谢大家的阅读!希望能够对大家有所帮助!