FPGA实现延时的方法有几种,下面介绍最常用的两种方法:

(1)如果只是作时序的延时,不需要准确定位,可使用门电路进行延时,比如使用两个非门进行延时。一个非门的延时时间大约为350ps到几ns之间吧,具体要根据不同厂家不同芯片的制造工艺,使用门电路进行延时也是比较常用的。

(2)使用时钟计数延时,这种方法可以精准延时,是FPGA使用得最多延时方法,很多时候时序逻辑都需要准确定位。

这种方法就是时钟周期计数,比如时钟为10MHZ,那么一个周期的时间为1/10000000=0.1μs。如需延时10μs则需计数100次,如需延时1ms则需计数10000次。

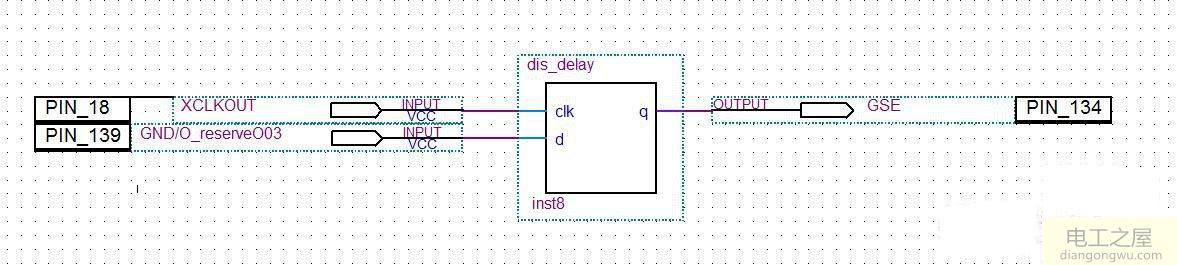

下面计数作延时输出的例子:clk为输入时钟(10MHZ),d为输入信号,q为输出信号,目的:将d输入的电平信号进行过滤延时,过滤5ms的脉冲,用于防抖处理。

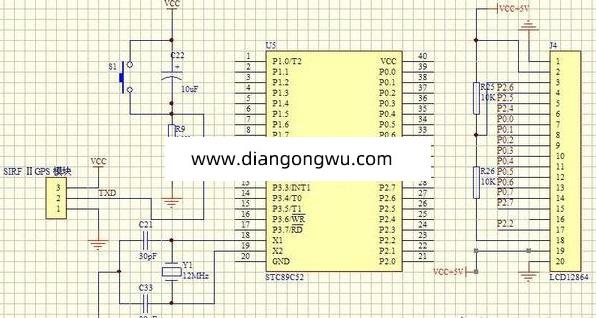

下图为综合后的模块图。

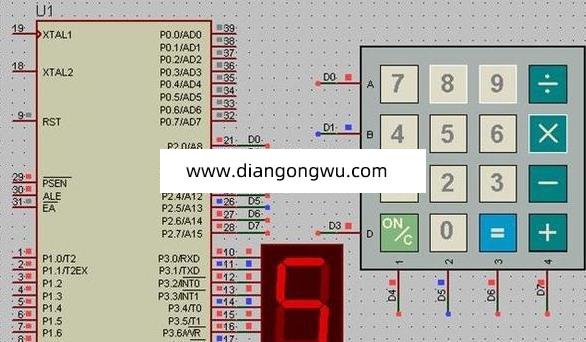

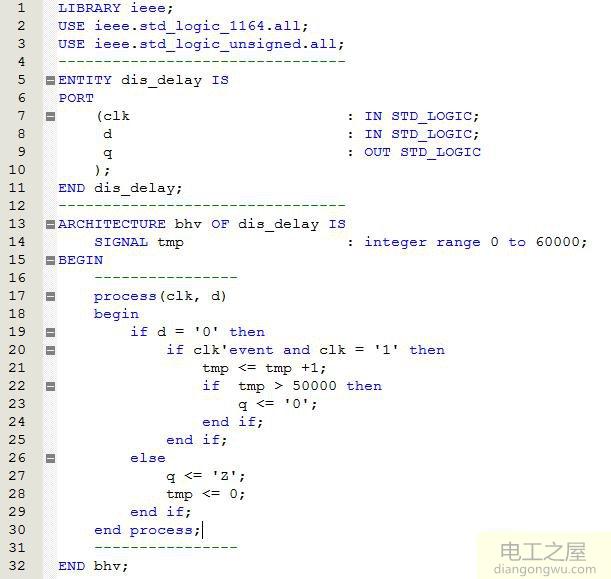

VHDL语言编程代码具体实现过程如下图所示,具有详细完整的代码。

当d为0时,开始记时钟周期数,计数大于50000次时,q的输出为0,否则为高阻态,50000个时钟周期正好是5ms。