根据要求,输入端口应该至少有两个(两个4位的二进制数据),输出至少一个。由于题目不够详细,比较后输出什么并没有说明,比如是数据1和数据2进行比较,若数据>数据2,输出1,否则输出0。或者是大于、小于或等于都应该输出不同的标志位。

下面以“数据1和数据2进行比较,若数据1>数据2,输出01;若数据1<数据2,输出10;若数据1=数据2,输出11。”进行举例设计。

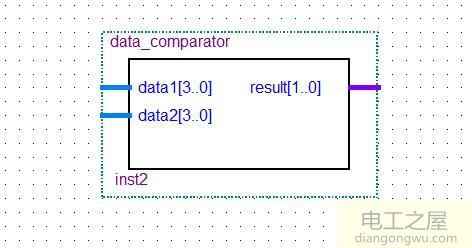

根据题目要求,输入端有两个:数据1和数据2,输出端有1个:结果。

本人比较喜欢使用Verilog HDL,跟C语言比较相近,通俗易懂,使用方便。

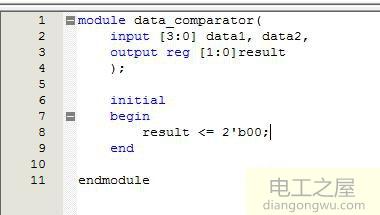

(1)首先,新建个工程,然后新建一个Verilog HDL File,先把模块名称(data_comparator)定义好,然后定义两个输入端data1和data2,一个输出端result,设置result的初始值为00,也可以不设置。模块的框架以关键字module开头,endmodule结束。

▲模块定义

(2)端口定义好之后就可以生成模块了,也可以完全编好程序之后再生成。生成的模块如下:

▲生成的模块符号

(3)最后把模块程序完善,always@(data1, data2)为触发语句,当data1或 data2数据有变化时就会往下执行。程序如下所示:

▲数据比较器模块程序

附代码:module data_comparator(

input [3:0] data1, data2,

output reg [1:0]result

);

initial

begin

result

end

always @(data1, data2)

begin

if (data1 > data2)

result

else if(data1

result

else if(data1 == data2)

result

else

result

end

endmodule