今天小编要和大家分享的是20进制计数器,计数器相关信息,接下来我将从20进制计数器设计方案汇总(三款仿真电路设计原理详细),《4.同步二进制加法计数器.pptx》这几个方面来介绍。

《4.同步二进制加法计数器.pptx》

本文为大家介绍三个20进制计数器设计方案。

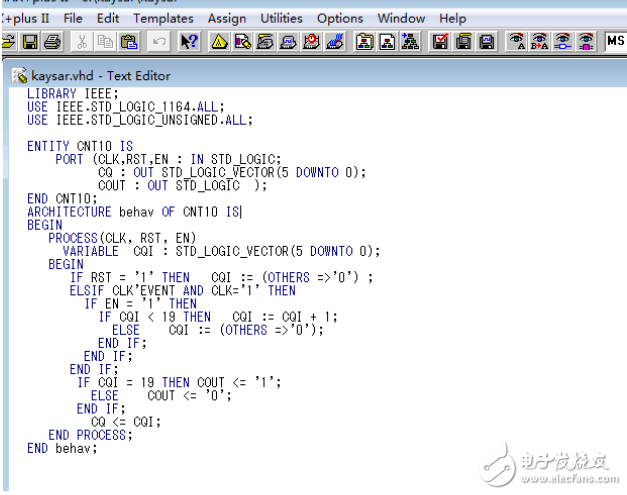

20进制计数器设计方案一:基于MAX+PLUSⅡ的20进制计数器设计

创建电路

文本图:

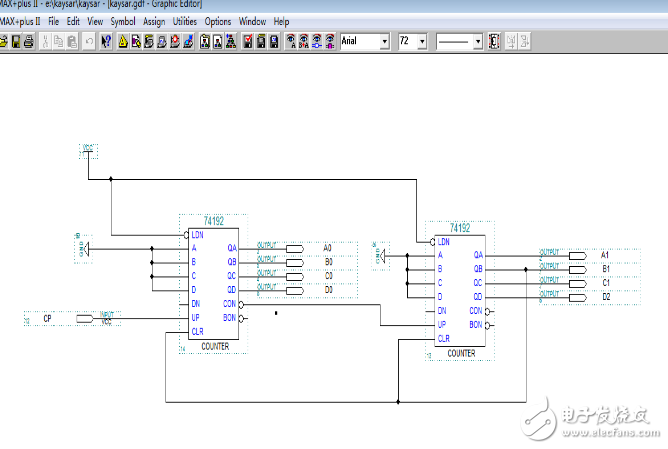

20进制计数器的原理图

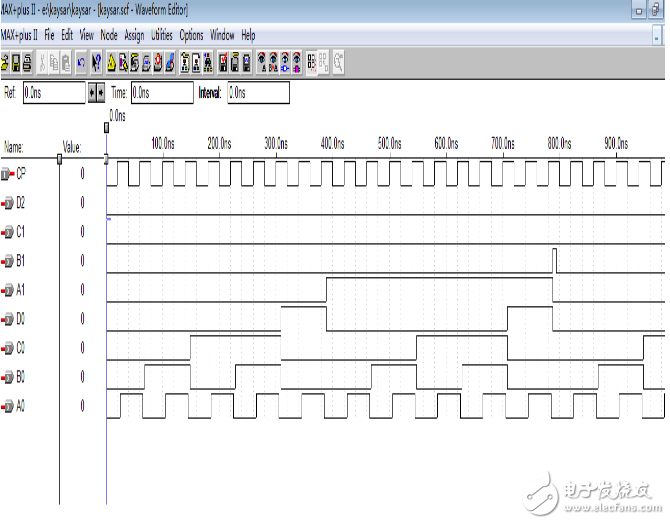

原理图输出波形图

可见当LD信号为“1”是不管CLK信号是什么都不工作。只要LD为“0”是才能正常工作。

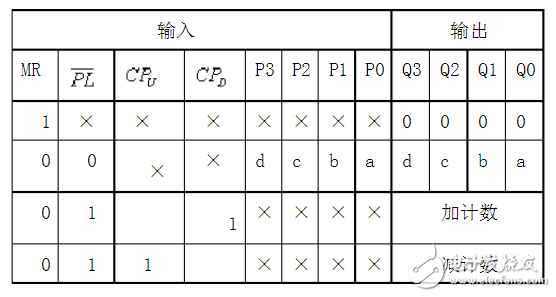

功能表

20进制计数器设计方案二:FPGA利用74161设计20进制计数器

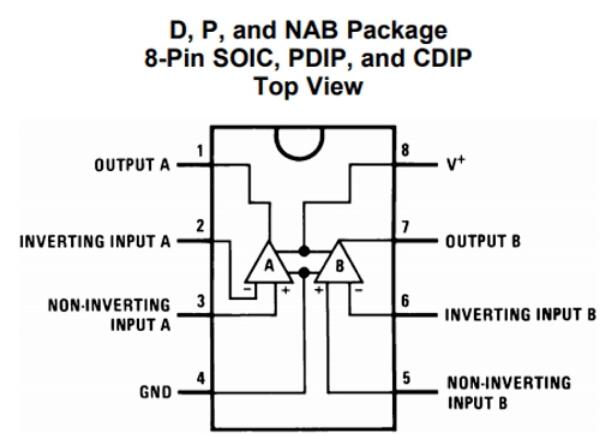

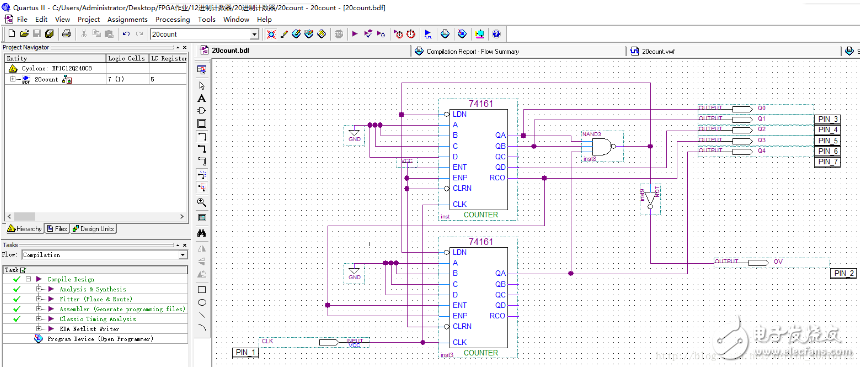

1.首先,建立工程,新建BDF文件,在BDF文件中画出电路图,如图所示:

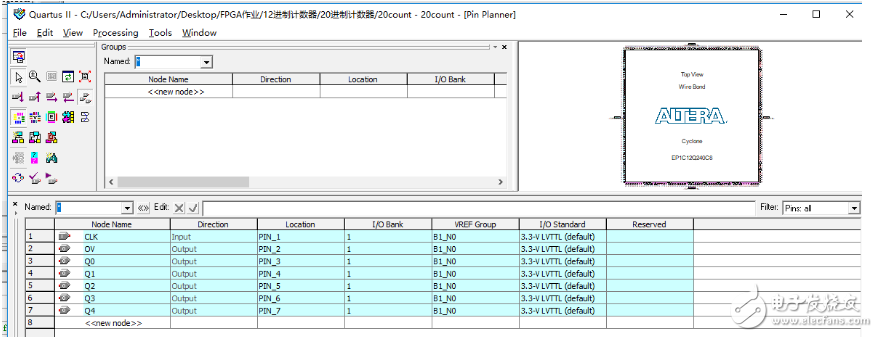

2.由于输入输出数目较少,PIN管脚设置采用手动输入的方法,设置后如图所示:

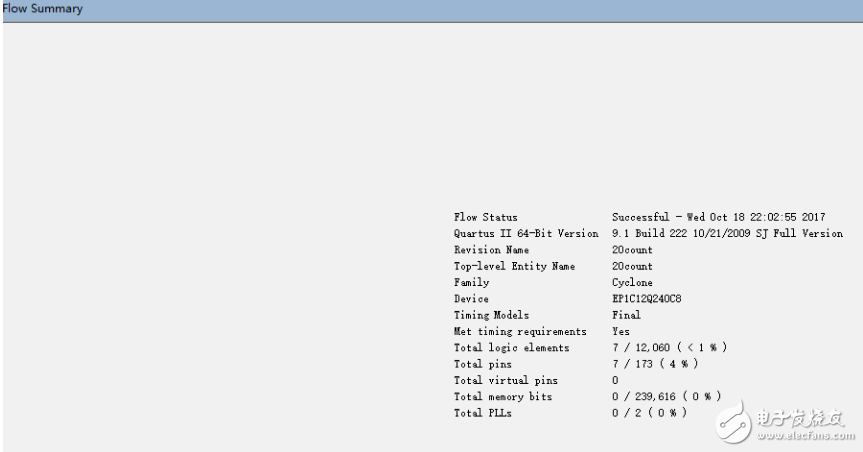

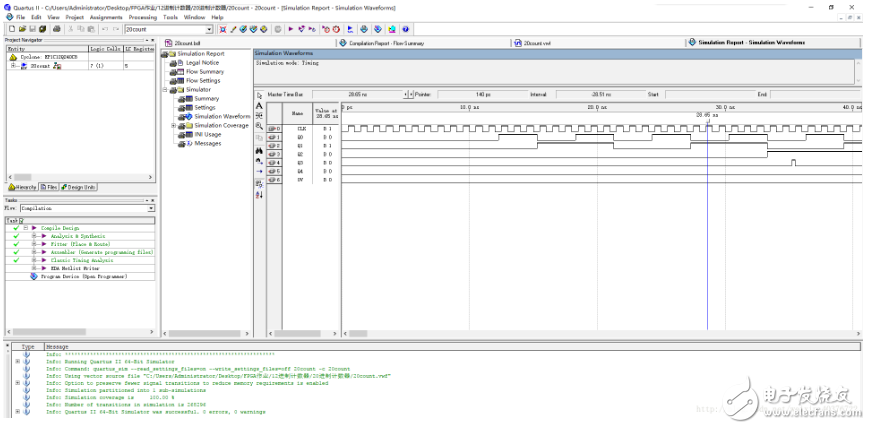

然后点击startcompilcation进行编译,得到如下结果:

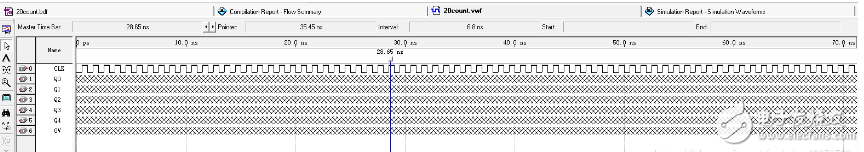

3.最后,进行仿真设计,先新建一个VWF文件,再将nodefinder中的关键引脚拖至仿真区,设置好仿真时间以及输入信号,如图所示:

点击startsimliation进行仿真,得到仿真结果如图所示:

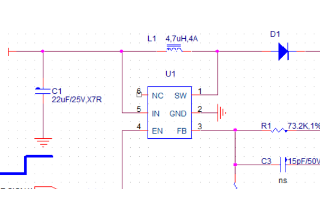

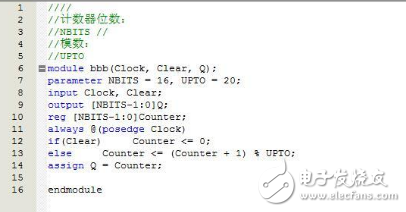

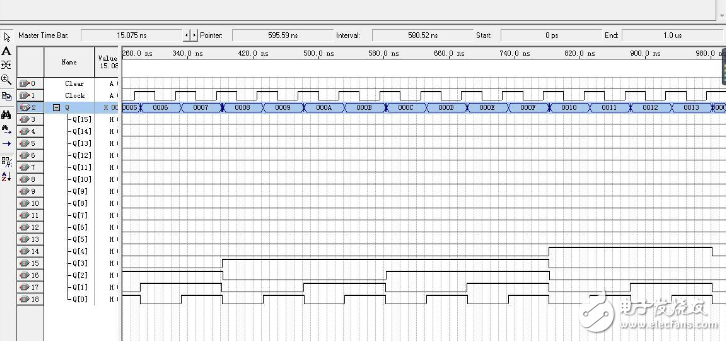

20进制计数器设计方案三:用verilog语言实现的20进制计数器

程序设计

仿真波形

关于20进制计数器,计数器就介绍完了,您有什么想法可以联系小编。