今天小编要和大家分享的是74ls161,60进制计数器,计数器相关信息,接下来我将从基于74LS161的60进制计数器设计方案介绍,三,实验原理 ① 集成四位同步二进制加法计数器74ls161 74ls161的逻辑这几个方面来介绍。

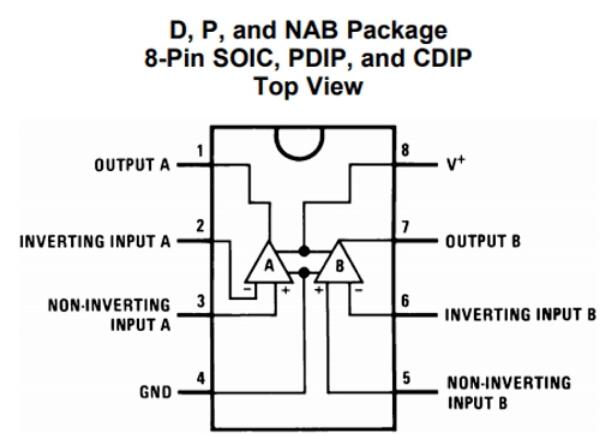

三,实验原理 ① 集成四位同步二进制加法计数器74ls161 74ls161的逻辑

计数器不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。但是并无法显示计算结果,一般都是要通过外接LCD或LED屏才能显示。

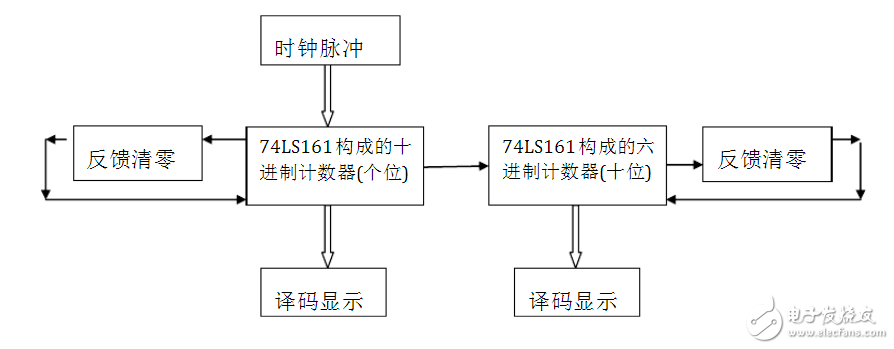

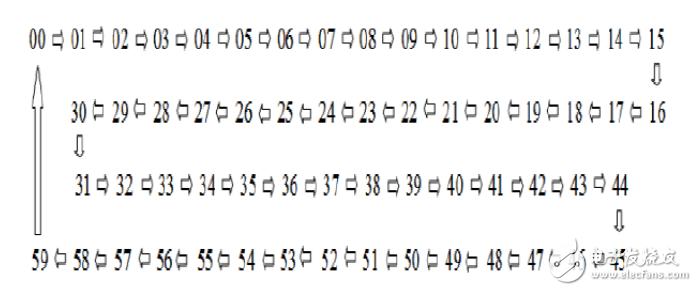

60进制计数器的工作框图和状态转换图

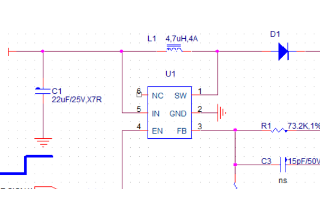

根据设计基理可知,计数器初值00,按递增方式计数,增到59时,再自动返回到00。因此,需要使用两片74LS161芯片级联的形式来构成六十进制计数器,一片控制个位,为十进制;另一片控制十位,为六进制。利用74LS161本身的控制端(完成十进制,在达到1001(即十进制的九)时),给高位芯片一个脉冲使高位芯片计数加一,同时低位芯片反馈清零,这样反复,直到第二片达到0110时第二片自身反馈清零,这样便完成一次60进制的计数,且回到初态,两片74LS161全部反馈清零,继续重复计数。图1、图2分别为60进制计数器的工作框图和状态转换图。

图1 60进制计数器的工作框图

图2 60进制计数器的状态转化图

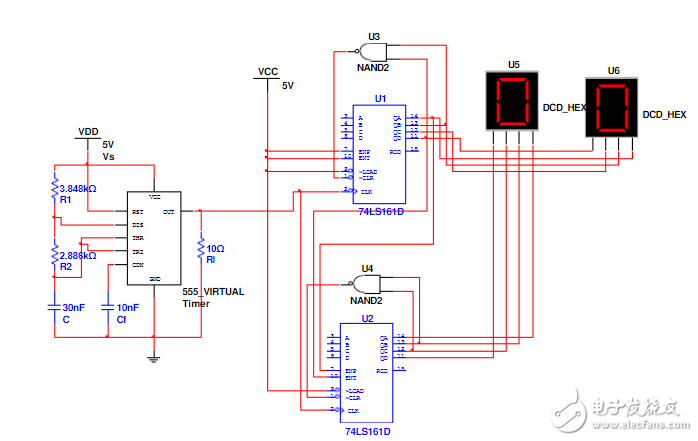

实施方案

制作60进制计数器,先要确定使用芯片个数。74LS161有16个状态,60进制计数器有60个状态,所以就需要两片74LS161串连并采用并行进位方式。具体电路连接图见图3。进行计数功能,将低位片的QD、QA连接到高位片的ENP、ENT,同时将低位片的LOAD、ENP、ENT管脚和高位片LOAD接到VCC=5V的电压源上,低位片和高位片CLK端共同接到时钟脉冲CP上。

U1为低位片(十进制计数器),U2为高位片(六进制计数器)。U2从“0000”状态开始,到“1010”状态后,这个状态“1010”通过与非门U3使CLR为低电平,此时U1清零。通过两片74LS161同步式连接,使得U2中的ENT、ENP为高电平,在下一个脉冲到来时,开始计数。U2有从“0000”状态到“0101”六个状态,下一个状态“0110”通过与非门U4,使得U2的CLR为低电平,U2清零。U1每10个状态,U2有1个状态。所以LED从00开始计数,显示59后,又从00重新开始。

图3 60进制计数器

关于74ls161,60进制计数器,计数器就介绍完了,您有什么想法可以联系小编。