今天小编要和大家分享的是74ls161,12进制计数器,计数器相关信息,接下来我将从74ls161构成12进制计数器设计,三,实验原理 ① 集成四位同步二进制加法计数器74ls161 74ls161的逻辑这几个方面来介绍。

三,实验原理 ① 集成四位同步二进制加法计数器74ls161 74ls161的逻辑

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。本文为大家介绍74ls161构成12进制计数器设计。

编辑推荐:74LS161中文资料pdf免费下载

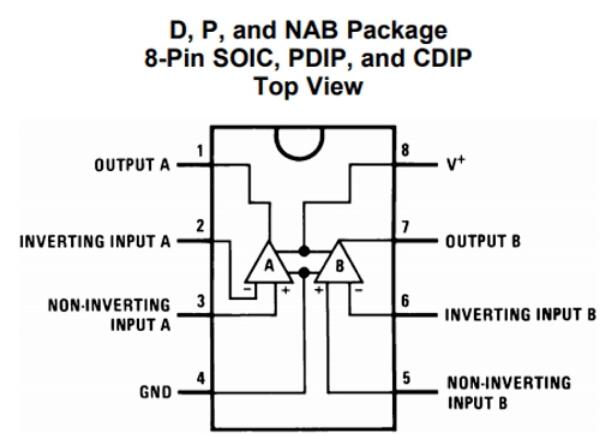

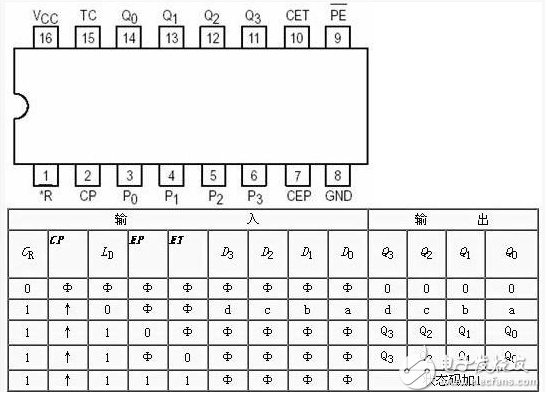

74ls161引脚图与真值表

管脚图介绍

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

74ls161功能分析

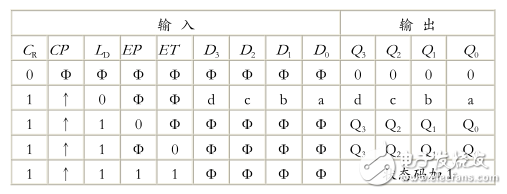

74ls161功能表

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。当CR=“1”且ID=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。74ls161还有一个进位输出端CO,其逻辑关系是CO=Q0.Q1.Q2.Q3.CET。合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

161的清除端是异步的。当清除端CLEAR为低电平时,不管时钟端CLOCK状态如何,即可完成清除功能。

161的预置是同步的。当置入控制器LOAD为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A-D相一致。对于54/74161,当CLOCK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而54/74LS161无此种限制。

161的计数是同步的靠CLOCK同时加在四个触发器上而实现的。当ENP、ENT均为高电平时,在CLOCK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。对于54/74161,只有当CLOCk为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLOCK 无关。

161有超前进位功能。当计数溢出时,进位输出端(RCO) 输出一个高电平脉冲,其宽度为QA的高电平部分。在不外加门电路的情况下,可级联成N位同步计数器。对于54/74LS161,在CLOCk 出现前,即使ENP、ENT、CLEAR 发生变化,电路的功能也不受影响。

编辑推荐:74LS161真值表

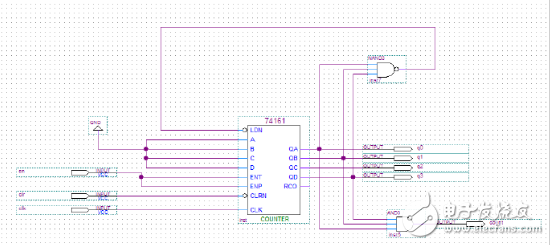

74ls161构成12进制计数器设计方案

74LS160是十进制计数器,要实现十二进制计数器必须用两片实现级联,把各位芯片预置1,当数码管显示9时,个位芯片开始进位即B端为0C端为1,经过与非门输出高电平,十位芯片开始工作,十位芯片由0变为1,此时十位芯片A端为1个位芯片B端为0C端为0,经过与或门输出0,十位芯片处于维持状态,当个位芯片显示2时,个位芯片B端为1十器位芯片A端为1,经过与非门输出0,重新开始预置数,即完成了十二进制计数。

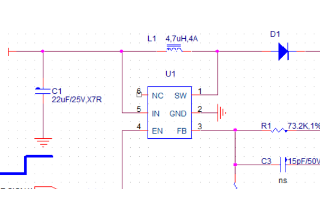

74ls161构成12进制计数器原理图

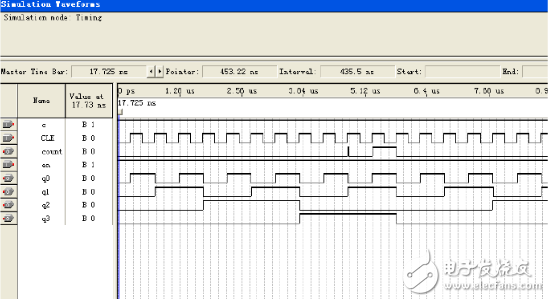

仿真波形图

关于74ls161,12进制计数器,计数器就介绍完了,您有什么想法可以联系小编。