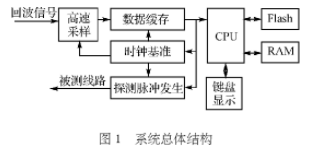

该仪器是一个便携式电缆故障检测设备,可利用现代电子技术(如高速A/D技术、异步FIFO技术、现场可编程逻辑阵列FPGA等)来提高集成度和灵活性。系统总体结构如图1所示。

脉冲发生电路产生探测脉冲,高速的A/D转换器对脉冲及其反射回波信号进行采样,使用异步FIFO作为A/D采样数据的缓存。软核Nios作为系统核心,控制检测任务的启动和结束、脉冲发送接收模式的选择、A/D采样数据的处理计算、故障性质和位置的判断及显示等。其中,软核处理器和逻辑功能都是在现场可编程逻辑器件中编程实现的。

2 功能及性能指标

短路测试:检测电缆芯线之间是否有不必要的连接及其位置。

断路测试:检测电缆中某芯线是否断路及其位置。

显示:显示测试结果,即测量中开路及短路的位置。

测量范围:2~1000 m。

测试精度:可选择2 m和10 m两种精度。

脉冲振幅:负载开路5 V。

脉冲宽度:20 ns,100 ns。

最大采样速率:100 MHz。

波形记录长度:1024点。

3 硬件设计

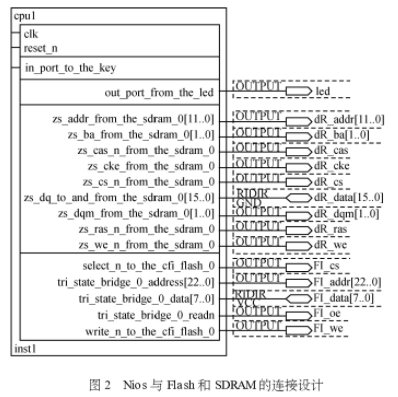

以Altera公司的Cyelone II系列FPGA器件EP2C20为核心,利用其Nios软核功能设计了微处理器,并完成了相关电路的设计。通过编程FPGA器件定制脉冲发生、高速时钟以及高速数据存储FIFO等模块,以此为基础设计了脉冲发送和接收电路以及高速数据采集和处理电路。

3.1 微处理器系统

简单来说,Nios是一种处理器的IP核,设计者可以将它放到FPGA中。Nios软核处理器是一种基干流水线的精简指令集通用微处理器,时钟信号频率最高可达75 MHz。采用Flash来存储启动代码和应用程序,当系统复位或加电启动时,Flash中的启动代码将被执行。采用SDRAM存储应用程序的可执行代码和数据,为程序提供运行空间。Nios软核与Flash和SDRAM的连接在FPGA中的设计如图2所示。