3.2 探测脉冲的产生

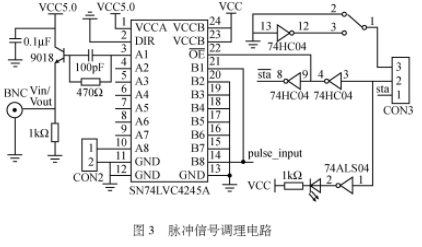

故障检测所用脉冲信号的宽度为20~100 ns,FPGA的工作时钟可以达到200 MHz,在其中生成减法计数器可产生满足脉宽要求的脉冲信号。减法计数器产生脉冲的幅度受限于FPGA的工作电平,对检测来说是不够的,因此从FPGA中出来的方波脉冲还要经过放大,才可以耦合到被检测线缆中去。脉冲信号调理电路如图3所示。SN74LVC4245A用作电平转换。sta和pulse_input均来自FPGA。

本设计采用的是5 V脉冲幅度,脉冲的馈送采取了晶体管射极驱动的方式。这种驱动方式比较简单,适用的器件也比较多。

3.3 A/D转换电路

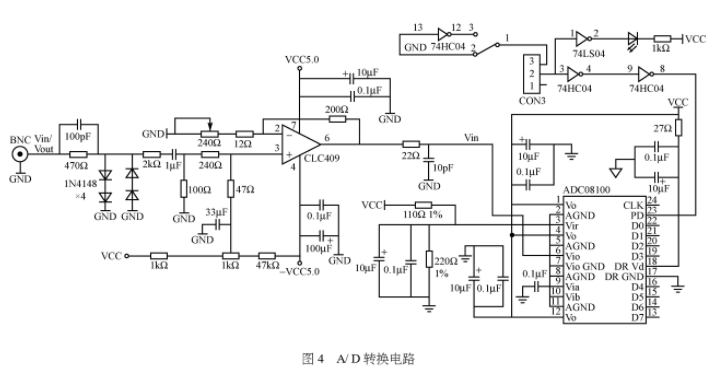

检测脉冲的宽度为20~100 ns,相应的数据采样率在20 MHz和100 MHz之间变化,一般的A/D芯片很难满足采样的要求,而用多片A/D芯片在成本和设计上都比较困难。这里选用美国NS公司的ADC08100,其采样速率为20~100 Msps,此时采样的功耗为1.3 mW/Msps,采样的功耗会随着采样时钟增加而增加,但是采样的特性不会受到影响,因此在采样率多样的系统中一个芯片可以起到多个芯片的作用。根据采样速率的不同,通过一个时钟控制模块产生相应的采样时钟信号,使芯片工作在所要求的速率之下,既可以节约成本,又可以简化设计。ADC08 100和FPGA配合使用,可以方便地改变采样时钟,具有很大的灵活性。

A/D转换电路如图4所示。探测脉冲及回波信号需要转换成适合A/D芯片电压水平的信号后再进行采样。脉冲在输入运算放大器之前进行了钳位处理,采用两组倒置的二极管并联,避免脉冲过高而击穿运算放大器。