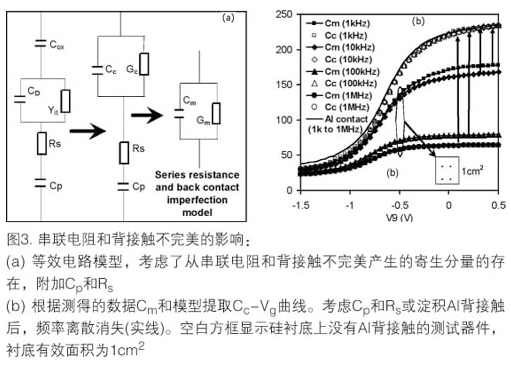

测得的电容可按照此模型校正而恢复,与测量频率无关,如图3(b)所示。串联电阻影响则可直接用在衬底背面淀积Al膜减至最小(图2(b)中的空心符号和图3(b)中的实线)。这表明,一旦考虑寄生分量时,有可能决定无误差的电容真值,保持测量系统的可靠性。

再研究高k MOS电路上损耗界面层的影响。在图1(b)中,要注意频率离散不是串联电阻影响引起的(因为此样品采用了有效面积大的衬底和Al背接触)。图1(a)中看到的频率离散缺失则可用高k层和界面层的相对厚度解释。图1(a)样品的界面层厚度(~1nm)与电容等效厚度(CET)~21nm比较可以忽略不计,这种情况下,高k层电容比界面层电容小得多(即Ch《《Ci)。但对于图1(b)的样品,尽管有Al背接触和较大的衬底面积,频率离散影响仍是很大的。此时Ch与Ci相当,将频率离散影响归因于界面层电容内的损耗(假定原始SiO2为~1nm),其中,缺陷是由界面位错和ZrO2/SiO2化学突变界面处键合配位中的固有差异引起的。

基于这一解释,图4(a)示出了采用双频技术做出的高k堆叠的4-元素电路模型,以便从损耗重建电容值。

图4(b)是校正后的C-V曲线,在三个完全不同的频率对上相互非常一致,证明模型在寻找电容真值方面是成功的。这表明,有损耗界面层也会影响高k堆叠中的频率离散。有损耗界面层对频率离散的影响也能用较密的SiO2膜(没有示出)替代原有SiO2或用厚得多的等效高k层(图1(a))加以抑制。