采用扫描设计技术后,在扫描控制端(SEN)和时钟端的控制下,通过扫描数据输入端,可以把需要的数据串行地移位到扫描寄存器单元中,串行地控制各个单元;同时也可以通过扫描输出端(Scan_out)串行地观测它们。这样就增加了时序电路的可控制性和可观测性。

2 扫描链策略设计

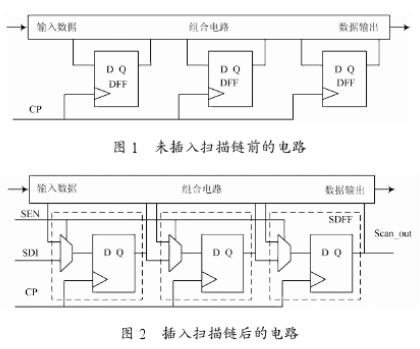

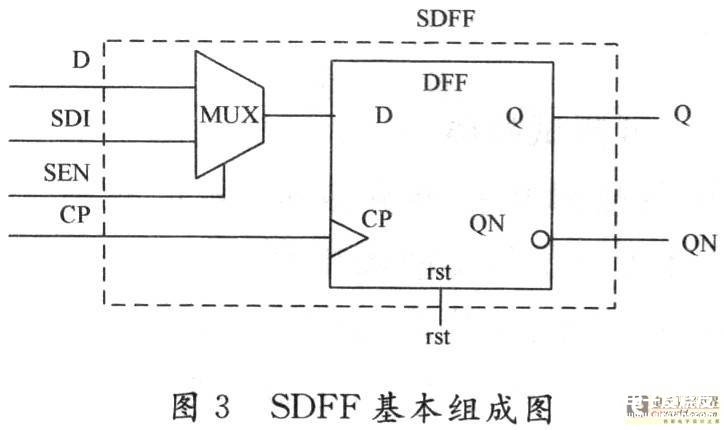

图2中虚线部分为扫描触发器,即扫描链的基本组成单元,其构成原理如图3所示。

扫描链设计前,电路中的触发器都是通过系统时钟端口控制数据的变化,因而在做扫描设计时可以通过系统时钟复用检测到更多的触发器,以此达到控制扫描触发器的目的。

同样的道理,一些特殊电路中的触发器也是采用手动或者软件的方法将它们串联到扫描链中,以此增加可扫描的触发器数,最终使故障覆盖率得以提高。但需要注意的是,这些可测性设计策略应用的前提是不能改变原始设计的功能。

3 设计中采用的策略

在进行DFT设计并插入扫描链的时候,最为重要的一个问题就是测试覆盖率,而它的最终值是由触发器的总数和最终能够测试到的触发器的数目的比值决定的,因此是否能够尽可能多地测试到本雷达芯片电路中的触发器,成为扫描路径法设计的一个关键问题。针对实际的设计电路提出了以下三种有效的设计策略,由最终测试结果可知,采用此设计策略后可大大提高测试覆盖率,满足设计指标需要。