3.1 时钟复用技术

每个触发器都受系统时钟控制,系统时钟能够覆盖本设计中大部分的触发器元件,因而考虑使用时钟复用技术,在插入扫描链进行测试时,把测试时钟引入到系统时钟上,这样测试时钟就能覆盖尽可能多的触发器,并在插入扫描链后,替换成扫描触发器。其实现原理如图4所示。

从图中可以看出,时钟电路产生很多不同频率的时钟以满足不同模块的需求,在时钟电路的输出端口加入相应的选择器(MUX)控制时钟的选择;当处于正常工作状态时,MUX选择正常的时钟进入相应的模块,进而实现相应的功能;当处于扫描状态时,这些MUX都是选择同样的扫描测试时钟信号(Te cp)进人到各个模块进行测试。这样做的优点在于不仅满足了测试选择的需要,而且也尽可能地测试到所有触发器,满足测试覆盖率的需要。

3.2 特殊时钟电路处理

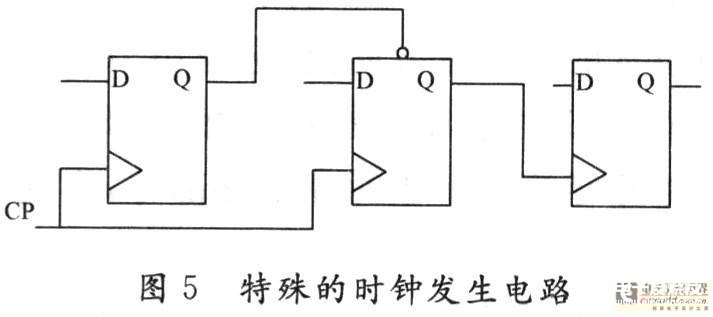

在本设计中存在很多特殊的电路,其中有一种时钟发生电路是不能进行扫描路径法的可测性设计,具体的电路图如图5所示。

在这种结构中,时钟从第二个触发器的Q端输出,输入到第三个触发器的时钟(CP)端。由于扫描时钟无法控制第三个以及后续的触发器,设计的扫描链将不会覆盖之后的电路,结果导致故障覆盖率降低,测试覆盖率也会下降。

改进此种电路结构的方法是手动或者用软件方式增加一个MUX选择器,当在扫描链插入时,正常的控制时钟信号就会进入第三个触发器的时钟端。具体实现的电路结构如图6所示。