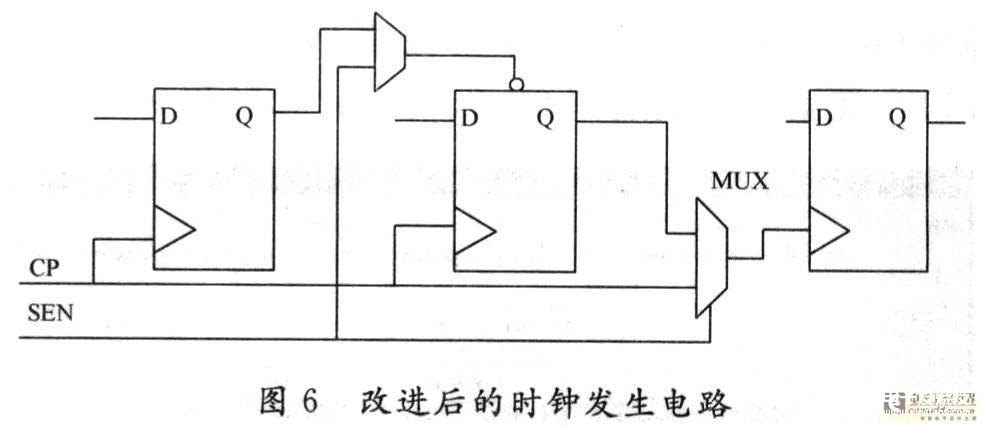

使用此策略,在插入扫描链后,当MUX选择器处在扫描状态时,扫描时钟就会连接到后续的触发器,并将其连接到扫描链上,这样就会大大提高故障覆盖率,从而提高测试覆盖率。

[page]

3.3 IP隔离技术

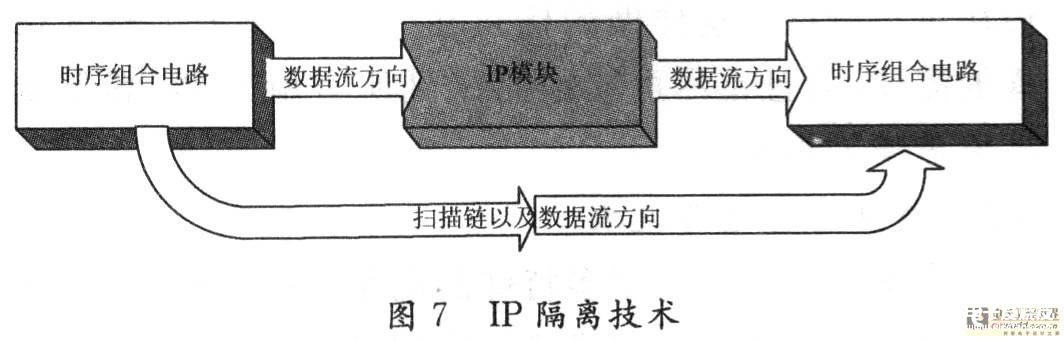

设计之中要用到很多IP模块,在综合后的网表中表现为一个个没有具体电路的“黑匣子”,这些“黑匣子”的存在使得部分时序组合电路不能或者很难进行基于扫描路径法的DFT设计,需要利用其他的DFT设计工具进行可测性设计,例如在本设计中采用的RAM和ROM存储器模块。

因此为确保与IP相连的下级时序电路部分能够被正常设计的扫描链覆盖,增加触发器的可测范围,采用的解决方案是用软件命令解决的方法将此类IP模块隔离,暂时不将此模块进行DFT设计,其实现原理如图7所示。

通过此种方法可以有效地将一个或多个类似的IP模块与原电路软隔离开。当电路工作在非扫描状态下,数据按照正常的数据流方向流、进流出IP模块;当电路工作在扫描状态时,扫描数据绕过相应1P模块,按照相应的扫描链路径流进下级时序电路部分,实现扫描测试的功能。

这种方法既不破坏原来芯片电路的结构和整体实现的功能,同时也保证了DFT设计的顺利进行,提高了本芯片可测性设计的覆盖率。

4 结果分析

4.1 测试结果

当没有采用任何设计策略时,本芯片的测试覆盖率只能达到30%~40%左右,远远达不到要求的性能指标。