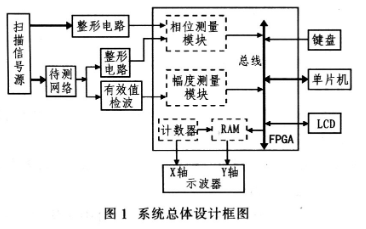

该系统以单片机和FPGA为控制核心,用DDFS技术产生频率扫描信号,采用真有效值检测器件AD637测量信号幅度。在FPGA中,采用高频脉冲计数的方法测量相位差,经过单片机运算,可得到100 Hz~100 kHz中任意频率的幅频特性和相频特性数据,实现在该频段的自动扫描,并在示波器上同时显示幅频和相频特性曲线。用键盘控制系统实现各种功能,并且在LCD同步显示相应的功能和数据,人机交互界面友好。图1给出系统总体设计框图。

4 理论分析与计算

4.1 扫频测试法理论依据

设频率响应为H(jω)的实系数线性时,不变系统在信号x(n)_Acos(ω0n+f)激励下的稳态输出为y(n)。利用三角恒等式,可将输入表示为2个复指数函数之和:

因此,输出信号和输入信号是频率相同的正弦波,仅有两点不同:第一,振幅被|H(ejω)|加权,即网络系统在ω=ω0的幅度函数值;第二,输出信号相对于输入信号有一个数量为q(ω0)的相位时延,即网络系统在ω=ω0的相位值。

4.2 DDS信号源

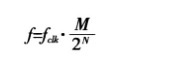

根据DDFS原理所产生的波形频率为:

式中fclk为基准频率,M为相位增量因子,N为累加器的位数。M取22,N取24。

为得到100 kHz的信号,而且在每个周期希望取到32个以上点,则累加器输出后级D/A转换需要至少3.2 MHz的速度,于是选取建立时间为30 ns、10位的DAC900,不仅满足了对D/A转换速度的要求,而且具有10位数据线,减少了D/A转换中固有的量化误差。fclk取40MHz,频率的最小步进: