采样过程中,数据的放大倍数与测量结果的同步时序控制是硬件需要解决的关键问题。数字滤波、数据分析计算和指数放大显示是软件需要解决的关键问题。

3.1 硬件相关

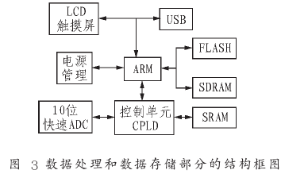

整个系统的结构包括数据采集、数据处理和数据存储,下面仅对部分关键技术进行讨论,随后描述控制单元的实现。

3.1.1 动态放大技术

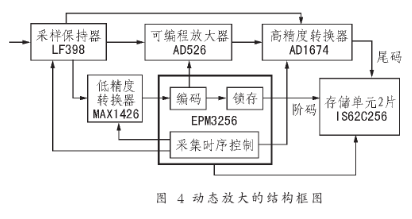

由于反射波幅值变化范围大,为了使小信号也有较高分辨率,采用硬件自动实时选择信号的放大倍数,增加系统的动态范围。在最大量程下,进行一次低精度A/D转换,控制单元CPLD(复杂可编程逻辑器件)读取转换值,编码存储进16位SRAM(2个IS62C256级联),并给放大器送出当前信号的增益系数。由于设计中采用二个可编程放大器AD526串接,增益为1、2、4、8、16、32、64、128、256九种,所以对于双极性信号,低精度ADC必须采用10位以上的模/数转换器才能满足所有增益的放大。选用MAXl426型10位模/数转换器作为低精度ADC,AD1674型12位模/数转换器作为高精度ADC,以降低开发成本。动态放大的结构框图如图4所示。

利用CPLD的硬件可编程特性,将数据的采样放大与模/数转换时序设定为流水线方式,高精度ADC转换数据时,浮点放大电路同步放大下一级信号。

后级12位ADC进行模/数转换时,前级的10位ADC又开始了下一轮数据的转换。在本设计中,12位高精度ADC转换的时间长于前级放大环节的时间,流水线的耗时主要在后一级上。

3.1.2 超前触发技术