通过对CS5321/CS5322的进一步研究发现,CS5322对SCLK要求的最小周期可以为100 ns,远远高于传统的设计方法所采用的移位时钟频率。因此,可以通过加快串行移位时钟(SCLK)来加快读出数据的速率,从而实现在一个采样周期内读出多道的数据。假设SCLK的频率为fb,则每道的24位的数据需要的移位时间为tm=24/fb,又采样周期为Ts=1/fs(fs可以为62.5 Hz、125 Hz、

250 Hz、500 Hz,1 kHz、2 kHz、4 kHz),fb的最大值可以达到10 MHz,只要适当提高fb就可以使tm《Ts,这样在一个采样周期里最多可以完成Ts/tm道数据传送,大大地提高了多通道数据采集传送的速度。例如,当fs=1 kHz,fb=1 MHz,则由以上分析可知,理论上一个采样周期里最多可以传送42个通道的串行数据。考虑到器件延时等多种因素,实际应用中应比此理论值小。

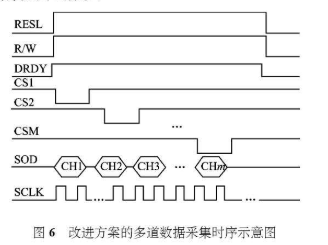

改进后的连线框图,是在图4的基础上去掉虚线部分,直接将第一通道的DRDY与FSR相连即可。改进方图6 改进方案的多道数据采集时序示意图改进后的多路∑一△A/D转换器同时进行卷积运算和数据转换,并几乎同时产生DRDY信号,但只有第一道的DRDY信号接到控制器的帧同步引脚(FSR),来触发处理器的串口接收1帧数据。各通道的片选CSl、CS2……CSm由控制器在一个采样周期里依次选中,各通道的SOD引脚都直接连接到控制器的DR引脚,整个系统的移位时钟可以由外部时钟源提供,也可以由控制器产生。

整个系统的数据采集过程如下:①初始化,启动A/D。②将A/D转换器的R/W置高电平,并设置采样率。③当DRDY变为高电平,同时使CSl有效,开始第一道数据采集;当24位数据全部接收完毕,第一道完成,使CS2有效,开始第二道采集,依次完成M道数据采集。④将数据存储并处理。