为了成为系统的一部份,eFPGA IP 必须具备易于整合于 SoC 的功能设计。Achronix 提供了可让客户直接整合于其 SoC 的 GDS II 版 Speedcore IP,以及可让客户用于设计、验证与编程 Speedcore eFPGA 功能的 ACE 工具客制版。

CPU 投片?

整个电子产业都知道 FPGA 极其热门。只要看看微软(Microsoft)的 Project Catapult 就知道了。

微软解释,这项计划是专为“加速微软在网络、安全、云端服务和人工智能(AI)等方面的超级运算基础”而打造的,并作为其于“后 CPU”(post-CPU)的各种技术——包括 GPU、FPGA 与 ASIC 的最大睹注。

微软这项 Project Catapult 的关键就在于 Altera Stratix V D5 FPGA。Mensor 强调,整个电子产业普遍存在的看法是,微软的计划促成了英特尔(Intel)决定收购 Altera。

藉由 AlphaGo,Googler 的客制 Tensor 处理器单元也激励了许多工程师,促使他们开始考虑从 ASIC 到 GPU 和 DSP 的一切。Mensor 解释说,他们正在寻找能够更有效率处理“加速非结构性搜寻、机器学习与人工智能”的技术。

Achronix 在其中看到了机会。

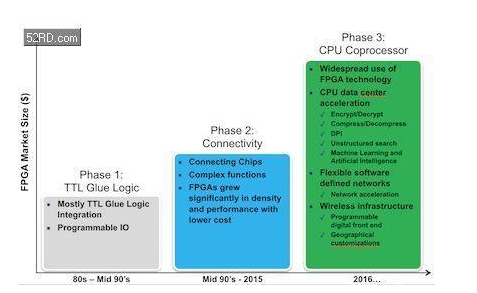

FPGA 从 1990 年代中期作为“胶合芯片”(glue chip)开始流行于市场上,如今正重新定义其价值,成为 CPU 的协同处理器。在这个角色上,FPGA 可加速加密 / 解密、压缩 / 解压缩,或甚至是预处理资料封包,以便只让有关的共享资料可被传送与进行处理。

当进行非结构化搜寻时,FPGA 的平行环境经证实是十分有效的。例如,相较于专为划分功能成为较小部份以及依顺序作业而设计的 CPU 而言,FPGA 能以平行方式,在单一频率周期完成整个任务。