寄存器堆regbank,RISC处理器的大部分指令通过寄存器来进行,所以寄存器的设计关系到整个体系结构,根据对体系结构的分析,需要设计32个通用寄存器。在FPGA设计中我们可以使用Xilinx的IP核生成器生成双口RAM[3],宽度为32,深度为32,一端只读,另一端支持读写。

译码单元控制着处理器各个部件的运行,通过对指令进行译码产生信号,控制各模块的操作,包括指令取指操作,寄存器堆存取操作,ALU操作,操作数选择,数据存储器访问和数据写回等。

指令存储器、数据存储器,是分别用以存放程序指令和数据的存储单元。在本设计中指令存储器以单口RAM IP核生成,并赋予初值,数据宽度为32位,深度为4096,即16KB大小。数据存储器也以单口RAM IP核生成,支持读写,写模式为只写,数据宽度为32位,深度为4096,即16KB大小。

取指逻辑包括程序计数器PC和地址加法器,主要完成从指令存储器读取指令和计算下一条指令的地址。

除了以上关键部件外,处理器还包括其它部件,如操作数选择单元,写回逻辑单元等。

4、 流水线设计

4.1 流水线

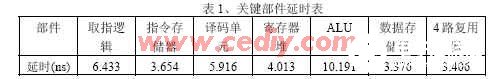

流水线是提高CPU处理速度的关键技术,为了提高指令执行速度,将整个执行过程划分为几个单元,各个单元完成固定部分工作,就像工厂的流水线作业一样。在流水线划分之前先对各处理关键模块通过综合工具进行大概的时延分析,在这使用ISE内嵌的综合工具XST,虽然XST在算术、功能等方面不如业界流行的综合工具Synplify Pro,但凭着对自己的器件熟悉,XST对Xilinx 芯片的支持是最直接。关键部件综合测试内部逻辑延时情况如下表1,从表中可以看到,最大延时部件是ALU(10.19ns),由于采用流水线,ALU源操作数据有多个选择,所以如果以ALU和数据选择器作为一个流水段,其他流水段的组合时延不超过这一阶段即可。经过分析,该流水线分为五段,即取指、译指、执行、访问存储器和写回五个阶段。预测系统时钟期为13.5ns。

4.2 流水线相关性问题及其解决

由于流水线的并行处理,产生指令相关性问题,一般存在三种相关:结构相关、数据相关和控制相关。在这主要讨论数据相关和控制相关二种。

数据相关,是指当一条指令的执行依赖于前面某一条未执行完指令执行结果时,这两条指令将发生数据相关。数据相关的解决通常有两种方法,一是推后分析法,即遇到数据相关时,推后本条指令的分析,直到相关的数据写入寄存器堆中;另一种是旁路技术(Forwarding)[4],即不必等到所需的数据写入到相关的寄存器中,而是经过专门设置的数据通路读取所需要的数据。这两种方法各有春秋,推后分析法容易设计,但因等待相关数据写入寄存器堆而引起了流水线断流;旁路技术(Forwarding),利用专用数据路径消除了一部分流水线断流,提高了处理器的速度,但要占用一定的逻辑资源。如果你的可编程逻辑芯片资源足够,采用旁路技术不失为一个提高处理器速度的好办法。本设计就是通过设置专用数据通路解数据相关,将前面相关指令还未写入寄存器堆的执行结果,提前提供给运算器使用,以减少流水线断流,但相关指令是load指令,并数据还没读出时,只能通过延迟一个周期以保证操作数的正确性。