控制相关,是指当执行到分支跳转指令时,因无条件分支目标地址还未计算出来,条件分支还未知条件是否成立等原因,而与后面的指令发生相关。控制相关问题的解决一般通过两方面来解决,一方面通过尽早判断分支条件是否成立和尽早计算出分支转移的PC值来解决,在本设计中,分支跳转条件的判断和分支跳转目标地址的计算,提前到译码阶段由专门的比较器和加法单元来完成,这样比在执行阶段进行条件判断和地址计算流水线可以减少断流;另一方面通过转移预测技术的硬件“猜测法”来解决,是指在当前还无法确定分支跳转指令的执行情况,无法确定下一条指令时,依据指令过去的行为来预测将来的行为。在本设计中通过选址单元猜测分支条件不成立,继续执行本指令的下一地址指令。猜测是否成功由译码单元决定,如果预测成功继续执行,否则重新取指并预取的指令无效。

4.3 流水线时序设计

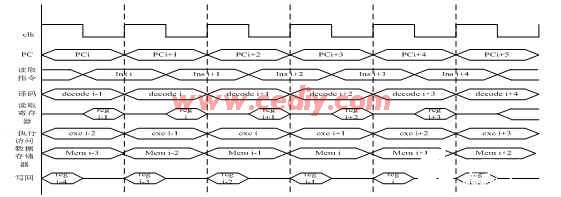

根据对各关键部件和流水线相关性的分析,设计系统流水线时序如图3所示。流水线的各个阶段在时钟上升时开始执行。取指阶段在时钟上升沿时读取程序计数器的指令地址,在本周期的时钟下降沿时从指令存储器读取指令。由于在同一周期内要对寄存器堆进行写操作和读操作,为了避免因数据带来的冲突,寄存器堆在前半周期进行写操作,后半周期进行读操作。

图3、系统时序图

4.4 流水线各阶段设计与实现

取指阶段,主要完成两个任务,一是根据程序计数器PC里的指令地址从指令存储器I_mem里读取指。另一个任务主要完成PC+1计算和下一条指令地址的猜测。对下一条指令的猜测主要是假设分支条件不成立,猜测下一条指令地址是本指令地址的下一地址,除了对下一条指令的猜测,还完成对上一次的猜测的确认。本指令地址的确认主要是完成如果上一条指令是分支指令时,如果分支条件不成立,本指令地址猜测是正确,指令有效,继续执行,否则本指令无效,重新再取指。

译码阶段,是整个系统中的关键控制阶段,不但进行指令译码,从寄存器堆中读取操作数,而且判断分支指令的跳转条件,计算跳转地址和处理数据相关性问题。这一阶段主要器件有译码单元,寄存器堆,加法器,比较器和地址选择器等。译码单元,可以说是核心控制单元,根据指令代码译码成各种控制信号控制各个单元的控制,而且进行数据相关处理。

译码单元,因采用旁路技术来解决数据相关性问题,因此在译码单元中参照前两条指令的目的寄存器号来确定是否发生数据相关性,如果发生数据相关,产生delay信号,使下一条指令重新取指。译码单元主要控制信号如下: