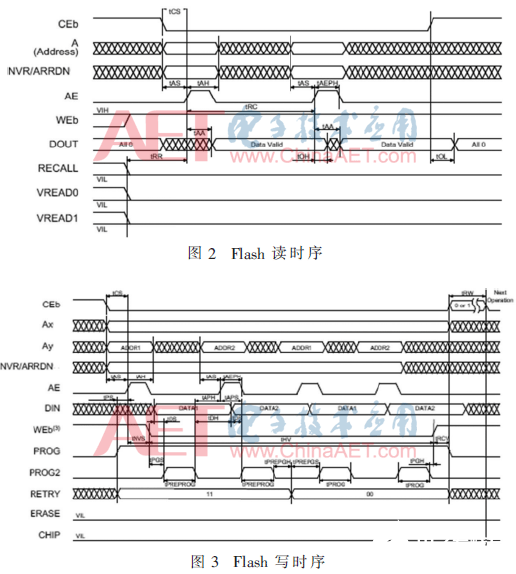

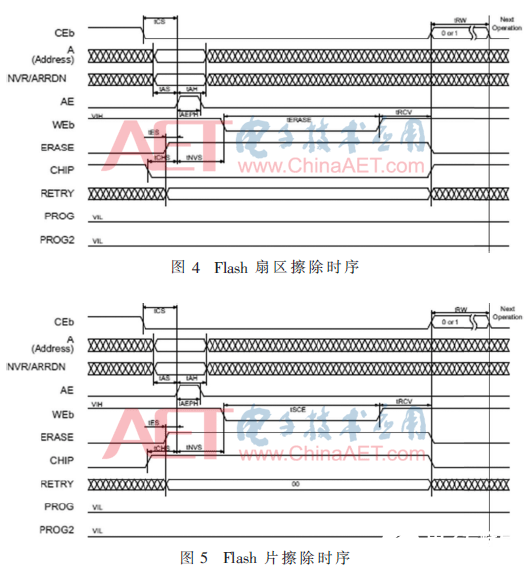

NOR Flash器件的操作分为读、写、扇区擦除、片擦除操作。时序图如图2~图5所示。

Flash读时序,发起AE脉冲锁定地址,tAA时间之后读出数据有效。

Flash写时序,先拉高PROG信号,然后AE脉冲锁定地址,产生PROG2脉冲写入对应数据。PROG拉高持续时间是tHV,也就是说写入时间是用户自己控制的。根据tHV的时间不同,可写入的word个数也不同。本文只讨论单个word的写入。

Flash扇区擦除时序,扇区擦除起始要用AE锁定扇区地址,拉起ERASE信号,执行擦除时序。ERASE时间由tERASE时间参数控制。

Flash片擦除时序,擦除起始要用AE锁定任意地址,片擦除除了拉高ERASE信号,还要拉起CHIP信号。ERASE时间由tSCE时间参数控制。

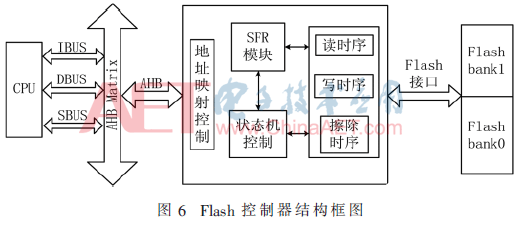

2 控制器方案

2.1 结构框图

Flash控制器模块在SoC系统中位于AHB matrix总线矩阵和Flash器件之间,CPU为ARM Cortex M4,总线为哈佛结构。CPU可以通过IBUS和DBUS对Flash器件进行访问。Flash控制器结构框图如图6所示。

Flash控制器实现了CPU对Flash器件的读、写和擦除。支持CPU在Flash中执行程序的同时可以对Flash其他区域进行擦写。Flash支持在大于1 MHz的多种频率下能对Flash器件进行擦写。

Flash控制器包含地址映射控制模块、SFR模块、状态机控制模块、时序转化模块。地址映射控制模块用于在线升级时对AHB访问地址进行映射;SFR模块用于Flash控制器的模式控制选择,配置和状态寄存器寄存等;状态机控制模块用于Flash控制器对各种模式的工作状态控制;时序转换模块用于根据状态机的当前状态来产生对应的Flash器件的时序。

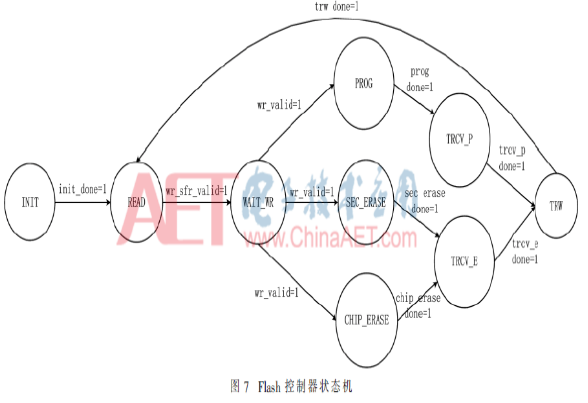

2.2 状态机设计

Flash控制器的状态机如图7所示,包含9个状态,INIT状态完成Flash上电启动,init_done之后进入READ状态。READ状态下支持AHB总线读操作。

如果要执行擦写,第一步则在READ状态下配置SFR模块的模式寄存器(PROG或者SEC_ERASE或者CHIP_ERASE),然后状态机跳转至WAIT_WR状态(注:在WAIT_WR状态也支持AHB总线读操作)。