第二步当AHB总线有写操作,则状态机跳转至对应的PROG或SEC_ERASE或CHIP_ERASE状态,开始对应的擦写时序转化。时序转化结束后,PROG跳转到TRCV_P,SEC_ERASE和CHIP_ERASE跳转到TRCV_E。之后跳转到TRW状态,结束后返回READ状态。

3 控制器实现分析

3.1 AHB总线数据相位扩展原理

AMBA AHB总线的写数据总线用来将数据从主机传输到从机上,而读数据总线用来将数据从从机传输到主机上。

AHB总线基本传输包含两个截然不同的部分:地址相位,只持续单个周期;数据相位,可能需要多个周期,这通过使用hready信号实现。

地址不长期有效,所以所有从机必须在这个时段(传输地址时)采样地址。然而,通过hready信号可以延长数据。当该信号为低时导致在传输中插入等待状态同时允许从机有额外的时间提供或者采样数据。

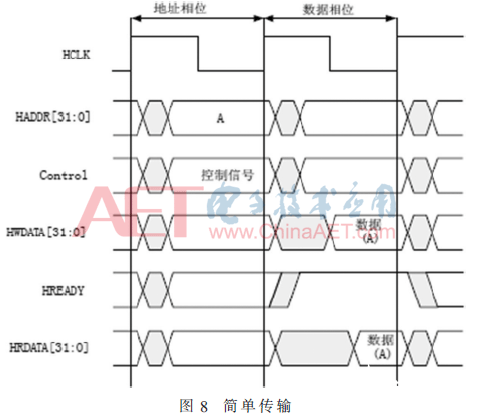

图8表示最简单的传输,没有等待状态。在这个没有等待状态的简单传输中,主机在HCLK的上升沿之后将地址和控制信号驱动到总线上;然后在时钟的下一个上升沿从机采样地址和控制信息;在从机采样了地址和控制信号后能够开始驱动适当的响应并且该响应被总线主机在第三个时钟的上升沿采样。

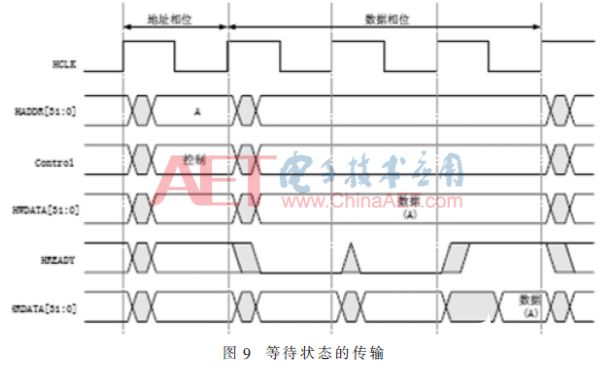

图9为具有等待状态的传输。从机插入等待周期(HREADY拉低)到任意传输中,这样扩展了传输完成允许的附加时间。对写操作而言,总线主机必须保持数据在整个扩展周期中稳定。

Flash控制器设计的擦写模式状态跳转利用了数据相位扩展阶段数据保持的原理。

3.2 SFR区的位置

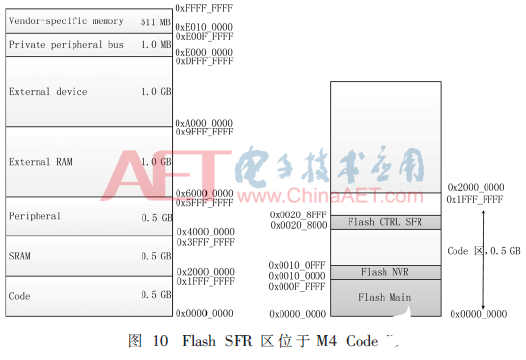

如图10所示,Flash擦写模式寄存器SFR区放在ARM cortex M4的Code区,Code区指0.5 GB以下,即小于0x2000_0000地址的空间,Code区只能IBus/DBus总线通过AHB接口进行访问。不放在Peripheral区APB总线访问,是为了避免IBus/DBus和SBus操作Flash的冲突。

以Flash写操作为例,如果模式寄存器放在Peripheral区APB总线访问,则CPU SBus配置完PROG模式寄存器(访问Peripheral区),准备开始PROG时序转换时,CPU IBus/DBus可能还在读取Flash操作中(访问Code区),这样控制器状态机需要等待判断读结束才能跳转,控制不好可能Flash的PROG写操作和读操作会冲突。