MVBC把来自于MVB总线的串行化信号转换为并行的数据字节,也把需发送的字节交由串行化电路发送到传输介质上。MVBC可根据配置实现总线主与总线从的功能,实现数据链路层以及一部分传输层的数据处理,并通过通讯存储器来与上层软件交互。总线控制器内部包含编码/译码电路和控制通信存储器所需的逻辑电路,用来控制帧的发送和接收(如冲突检测、帧的前导比特处理、CRC校验位的处理等);对输入帧译码并检验其有效性;把数据存放到相应的通信存储器中。

3、 帧收发器的设计

MVBC中的帧收发器主要负责帧的发送、接收,包括曼彻斯特码的编码、解码,CRC(循环冗余检测码)的产生与校验,不同类型帧的构建与识别,以及码错的识别和冲突的检测等。其中曼彻斯特编解码以及CRC校验为主要的算法。

3.1 曼彻斯特编码、解码器的设计

MVB总线上的串行数据采用曼彻斯特码,曼彻斯特编码中的每个数据位应用以下规范编码:

a)一个“1”的编码在位元的前半部分位“高”,后半部分为“低”;

b)一个“0”的编码在位元的前半部分位“低”,后半部分为“高”;

如果曼彻斯特码中出现整个位元的高电平(NH)或整个位元的低电平(NL),则被认为非数据符,用于特殊场合,如:帧头,帧尾标识。

(1)曼彻斯特编码器

根据曼彻斯特码的编码要求,曼彻斯特编码器其电路实现如图2-5所示:

串行数据在1.5M时钟的上升沿处从上一级的移位寄存器输出,在高、低电平时与1.5M时钟相异或,结果得到与上面编码规则相符的曼彻斯特码。

(2)曼彻斯特译码器

曼彻斯特译码过程主要是将串行曼彻斯特码转变成串行的电平信号,并把串行电平信号组合成并行信号输出,以便进一步处理。如果输入的码字不符合曼彻斯特码编码规则(由冲突或其它原因引起),译码器将报告错误信息。

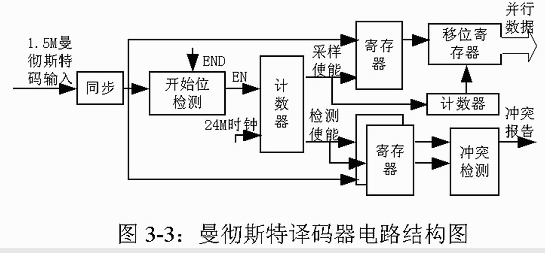

曼彻斯特译码器设计电路如图3-3:

曼彻斯特码输入后经过三级寄存器同步,消除亚稳态。如果总线在空闲状态之后出现下降沿,则被认为帧的开始位,总线上再出现高电平时使能16位计数器计数。如果把曼彻斯特码每个bit周期分为16个部分,如图3-4: