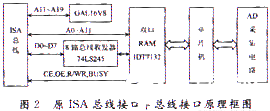

原ISA总线接口卡总线接口原理框图如图2所示。

4.2 PCI接口卡的设计和实现

为了实现PCI总线接口需在原ISA接口板上加上CH365芯片及其周边电路。CH365芯片与PCI总线的连接符合PCI总线规范,而CH365芯片提供的本地总线接口端与ISA总线接口类似。为了减少总线接口改变带来的改动,本文利用CH365芯片的本地硬件地址功能设定接口卡的本地硬件地址。

4.2.1 本地硬件地址功能的实现

CH365提供一种可以由板卡制造商选定PCI设备I/O口地址的方法,即本地硬件定址,其原理是将PCI设备的部分I/O口地址译码,通过外围的二级译码电路来实现。外围的二级译码电路比较简单,与ISA总线的I/O译码电路类似,CH365将PCI总线I/O操作地址同步提供给外围电路,当外围电路对地址译码匹配后,向CH365请求本地硬件定址,再由CH365请求PCI总线在该特定I/O口地址范围内进行读写操作。

为启用CH365提供的本地硬件定址功能,需将CH365局部数据总线端中D4线弱下拉接地(即设定值=0),以设置CH365工作于本地硬件定址模式。外围二级译码电路可由GAL16V8实现。

4.2.2 双口RAM的读写

CH365的本地地址线和数据线端与双口RAM相连。双口RAM允许2个CPU同时读取任何存储单元(包括同时读同一地址单元),但不允许同时写或一读一写同一地址单元,否则就会出现写入值和读出值不是期望值的混乱状态。虽然双口RAM本身带有BUSY控制信号来协调两端的访问,但BUSY信号脚要求与两侧CPU的READY线相连,而CH365并不具有READY信号线,因此,需要引入仲裁逻辑控制模块。常用的双口RAM解决地址竞争的途径有:令牌传递法、基于邮箱机制的INT中断法以及插入等待周期的BUSY法等。在本系统中采用第二种方法。

基于邮箱机制的INT中断法的基本思想是:给每个端口分配一个地址作为邮箱,比如本系统可以令CH365使用00H,单片机使用8000H,这两个地址用来装载作为分配两端口RAM使用权的依据数据。具体约定为:当左端口CH365写地址单元00H时,通过逻辑器件可实现右中断DSP INT(DSP中断)为低,向DSP发出中断清求,DSP读地址单元00H时,DSP INT为高,复位CH365发出的中断请求。同理,当右端口写地址单元8000H时,左中断INT REQ(CH365中断)为低,可向左端口发出中断请求;而当左端口读地址8000H时,INT_REQ为高,复位DSP发出的中断请求。当信箱内容为00时,表示正在使用该方端口;当信箱内容为FFH时,表示结束使用该端口。因此,双方在对端口的其他单元进行读写操作开始时,需要向邮箱中写入00H,操作结束,写入FFH。如果没有发生争用,则直接进行读写操作,否则,慢的一方产生中断,并查询对方邮箱,直到对方邮箱内容为FFH。具体实现可借助CPLD来完成。