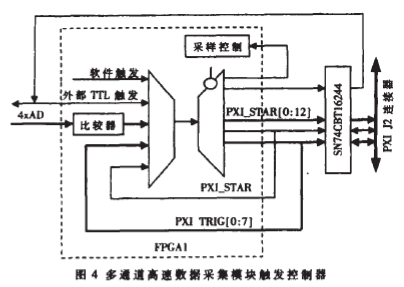

PXI仪用模块的触发源有:用于不同仪器同步的外部TTL触发源(同步触发或异步触发)、外部模拟电平变化触发源(上升沿触发源或下降沿触发源)、PXI_STAR触发源、PXI TRIG触发源、软件触发源等。多通道高速数据采集模块通过PXI_STAR总线或PXI TRIG总线传送给其他模块或通过外部双向触发信号线传送给其他仪器的触发源采用PXI同步触发,由于采样时钟频率远高于PXI_CLK10频率,在不违背PXI同步触发时序要求的前提下,同步触发的参考时钟可以是仪用模块的时基,这样构建的综合测试系统的同步精度可以达到理想的情况。多通道高速数据采集模块的触发结构如图4所示。最终处理的触发信号送给FPGA1中的采样和存储控制模块,有选择地通过PXI触发总线送给其他PXI模块,以及通过外部触发信号送给其他仪器。

此外,根据相对于事件的同步时机的不同,触发分为负延迟触发(Pre-trigger)、零延迟触发(Post-trigger)、正延迟触发(Delay-trigger)等模式,通过硬件和软件共同实现。实测表明,当信号发生器的同一个信号输出到不同采集模块上,在不同触发模式下,其波形在时间上完全重合,达到了仪器的同步要求。

4 、EMC设计

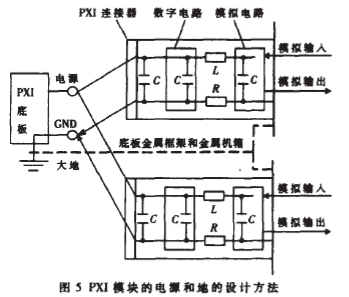

PXI是个仪用平台,对机箱环境已经做了充分的EMC设计,PXI底板通过PXI J1、J2连接器向PXI模块供电。PXI模块通常分为模拟和数字两个部分,模拟部分靠近前面板,数字部分靠近PXI连接器。为了增强PXI仪用模块的抗干扰性能并避免对其他模块的干扰,PXI模块还需要针对PXI机箱的结构特点精心设计电源,特别是参考地平面的安排。

由于仪用模块通常是模/数混合电路,将模拟地与数字地隔离,模拟地与前面板相连,则数字电路的电流回路通过PXI连接器回到底板地,模拟电路的电流回路只能通过前面板→PXI底板的金属框架(或者金属机箱)这一通路直接流回大地,有效地避免了数字电路通过电源或地对模拟电路的干扰,如图5所示。但两个地若完全隔离,热拔时前面板与PXI底板和机箱的联结将脱离,模拟电路的电流回路断开,造成静电无法释放,因此在两个地平面之间串上一个比数字地到底板地之间的阻值高得多的电阻来解决模拟电路的静电释放问题,这个电阻值通常在10Ω~100kΩ之间选择。模拟电源采用π型滤波,电感两端的解耦电容分别与数字地和模拟地相连。

电源和地平面的精心设计以及其他EMC技术在设计中的应用可以将噪声限制在很低的程度,实测表明,模拟电路的系统噪声只有±1LSB,即±0.09mV。