(3)PXI提供了一个超高性能的星形触发总线,同参考时钟一样,星形触发信号是由位于第一外设槽的星形触发控制器将信号点对点沿着等长的信号线传送给其他外设槽,其信号抖动小于1ns,覆盖两个总线段。

对于PXI仪用模块的设计,应考虑其在综合测试系统中的应用,前面板至少需要一个时钟输入、一个双向触发线,结合仪器本地自洽的时钟和触发总线,方能建立一套完备的同步机制。

3.1 PXI仪用模块精密时基的设计

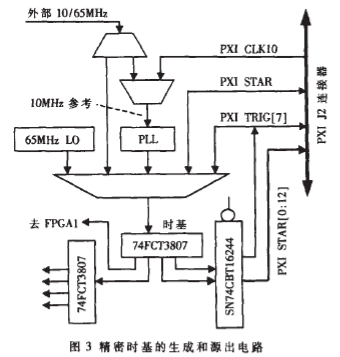

通常一个PXI仪用模块应有三个时基源: PXI_CLK10参考时钟、外部(前面板)10MHz参考时钟或65MHz时基、PXI_TRIG[7]或PXI_STAR提供的采样钟。模块精密时基的设计包括时基的生成和传送。由于A/D转换器的采样时钟频率为65MHz,所以模块的时基频率可以定为65MHz。如果利用10MHz参考时钟,还必须通过PLL进行倍频,显然倍频系数不是整数。当不同的模块利用PXI_CLK10获取65MHz采样钟作为时基时,不同模块间的采样钟很难达到相位同步。为了保证所有模块同步,如前所述,可将这个采样钟通过PXI_TRIG、PXI_STAR[0:12]传送给其他外设槽。对于多台仪器的同步应用,最好通过用户前面板由外部提供时基源。

由于有多个时基源,且通常时钟的电平是TTL电平,可采用5V耐压的电平转换多路复用/解复器进行选择。这里选用SN74CB3T3253和SN74CBT16244,其传播时延均小于0.25ns。EP1C6Q248内部有两个PLL,一个PLL用来从10MHz参考钟获取时基,一个用于获取数据传输和SDRAM控制器的80MHz时钟。精密时基的获取和源出电路如图3所示。时基源的选择和时基信号的源出由用户通过软件进行配置。

3.2 触发控制器的设计

除了上述的精密时基,仪器同步机制的另外一个关键是触发系统。不论是简单测试系统还是综合测试系统,一个测试系统的动作起点(epoch)依赖于一定的事件。事件有简单的,如一个信号电平的变化,较为复杂的是多个信号的组合变化,如熟知的逻辑分析仪。对于综合测试系统,激励信号和测试信号就更多,而且是相互关联的,一般意义上,激励信号集和测试信号集可以用状态空间来描述和分析,而事件就是状态空间的某种迁移,单个信号的变化和数个信号的组合变化则是状态空间迁移的特例。在对同一个被测对象进行测试时,为保证仪器的某个模块上所发生的事件能同时通知到其他模块或仪器,通常采用一套硬件触发机制或精密时钟协议来实现,如最新架构的LXI仪器采用PTP来实现仪器的同步。实际上硬件触发机制只有硬件延迟,而采用协议实现同步的仪器的精度很难做到ns级,如LXI的同步精度为亚微秒级,故LXI规范仍保留了硬件触发机制即A类LXI来满足对同步精度要求较高的应用。PXI是通过硬件触发机制来实现仪器同步动作的,通过PXI_STAR总线、PXI TRIG总线实现仪器系统中各模块发生的事件的相互通知。根据触发电路的实现方式不同分为PXI同步触发和PXI异步触发,同步触发的参考钟为PXI_CLK10,有一定的时序要求。