支持多个总线主设备控制器;

支持猝发、分裂、流水等数据传输方式;

单周期总线主设备控制权转换;

32~128位数据总线宽度;

具有访问保护机制,以区分特权模式和非特权模式访问,指令和数据读取等;

数据猝发传输最大为16段;

地址空间32位;

支持字节、半字和字传输。

AMBA的ASB适用于高性能的系统模块。在不必要适用AHB的高速特性的场合,可选择ASB作为系统总线。它同样支持处理器、片上存储器和片外处理器接口与低功耗外部宏单元之间的连接。其主要特性与AHB类似,主要不同点是它读数据和写数据采用同一条双向数据总线。

AMBA的APB适用于低功耗的外部设备,它已经过优化,以减少功耗和对外设接口的复杂度;它可连接在两种系统总线上。其主要特性如下:

低速、低功耗外部总线;

单个总线主设备控制器;

非常简单,加上CLOCK和RESET,总共只有4个控制信号;

32位地址空间;

最大32位数据总线;

读数据总线与写数据总线分开。

2 、Wishbone总线

Wishbone最先是由Silicore公司提出的,现在已被移交给OpenCores组织维护。由于其开放性,现在已有不少的用户群体,特别是一些免费的IP核,大多数都采用Wishbone标准。

Wishbone总线规范是一种片上系统IP核互连体系结构。它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度。Wishbone总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容已有所有的综合工具,可以用多种硬件描述语言来实现。 Wishbone总线规范的目的是作为一种IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口。

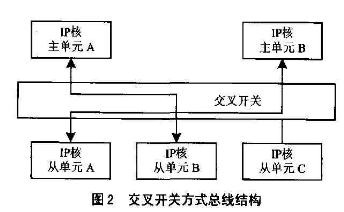

Wishbone总线结构十分简单,它仅仅定义了一条高速总线。在一个复杂的系统中,可以采用两条Wishbone总线的多级总线结构:其一用于高性能系统部分,其二用于低速外设部分,两者之间需要一个接口。这个接口虽然占用一些电路资源,但这比设计并连接两种不同的总线要简单多了。用户可以按需要自定义Wishbone标准,如字节对齐方式和标志位(TAG)的含义等等,还可以加上一些其它的特性。Wishbone的一种互连结构如图2所示。

灵活性是Wishbone总线的另一个优点。由于IP核种类多样,其间并没有一种统一的间接方式。为满足不同系统的需要,Wishbone总线提供了四种不同的IP核互连方式: