点到点(point-to-point),用于两IP核直接互连;

数据流(data flow),用于多个串行IP核之间的数据并发传输;

共享总线(shared bus),多个IP核共享一条总线;

交叉开关(crossbar switch)(图2),同时连接多个主从部件,提高系统吞吐量。 还有一种片外连接方式,可以连接到上面任何一种互连网络中。比如说,两个有Wishbone接口的不同芯片之间就可以用点到点方式进行连接。

Wishbone总线主要特征如下:

所有应用适用于同一种总线体系结构;

是一种简单、紧凑的逻辑IP核硬件接口,只需很少的逻辑单元即可实现;

时序非常简单;

主/从结构的总线,支持多个总线主设备;

8~64位数据总线(可扩充);

单周期读写;

支持所有常用的总线数据传输协议,如单字节读写周期、块传输周期、控制操作及其它的总线事务等;

支持多种IP核互连网络,如单向总线、双向总线、基于多路互用的互连网络、基于三态的互连网络等;

支持总线周期的正常结束、重试结束和错误结束;

使用用户自定义标记(TAG),确定数据传输类型、中断向量等;

仲裁器机制由用户自定义;

独立于硬件技术(FPGA、ASIC、bipolar、MOS等)、IP核类型(软核、固核或硬核)、综合工具、布局和布线技术等。

3 、Avalon总线

Avalon总线是Altera公司设计的用于SOPC(System On Programmable Chip,可编程片上系统)中,连接片上处理器和其它IP模块的一种简单的总线协议,规定了主部件和从部件之间进行连接的端口和通信的时序。

Avalon总线的主要设计目的如下:① 简单性,提供一种非常易于理解的协议;② 优化总线逻辑的资源使用率,将逻辑单元保存在PLD(Programmable Logic Device,可编程逻辑器件)中;③ 同步操作,将其它的逻辑单元很好地集成到同一PLD中,同时避免复杂的时序。

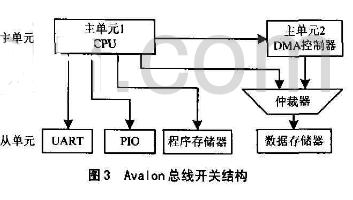

传统的总线结构中,一个中心仲裁器控制多个主设备和从设备之间的通信。这种结构会产生一个瓶颈,因为任何时候只有一个主设备能访问系统总线。Avalon总线的开关构造使用一种称之为从设备仲裁(Slave-side arbitration)的技术,允许多个主设备控制器真正地同步操作。当有多个主设备访问同一个从设备时,从设备仲裁器将决定哪个主设备获得访问权。图3是一个多主设备同时访问存储器的例子。在此系统中,高带宽外设,如100M以太网卡,可以不需暂停CPU而直接访问存储器。通过允许存储访问独立于CPU。Avalon开关结构优化了数据流,从而提高了系统的吞吐量。