3 PC体系下的中断

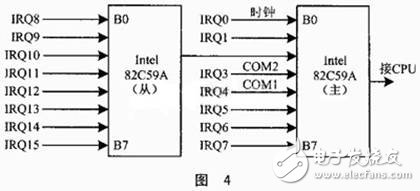

X86系列的处理器可支持256个中断,并用向量表的方法来关联每个中断和相应ISR的位置。在实模式下,中断向量表(IVT)存于内存的低端1K。每个向量表条目占4字节,保存一个ISR的段地址和偏移信息。PC系统使用两个级联的可编程中断控制器82C59A。一个82C59A能连接8个硬件中断,编号为IRQ0~IRQ7。 PC总共可管理15个外部中断源,PC的中断控制器如图4所示。(关于82C59A的详细使用可参见有关资料。)

在μC/OS下,CAN总线I/O端口中断向量设置伪代码:

void CanInitHW(UI segment,BYTE Irq0,BYTE Irq1){

保存原有的中断向量

保存掩码寄存器的值

使82C59A的掩码寄存器(0x21)各位置1,关闭中断输入

关闭CPU中断

设置新的中断向量

正在服务的中断禁止再次响应服务(假定当前服务中断是IRQ5)

开CPU中断

清除82C59A的掩码寄存器(0X21、0XA1)各位,开启中断输入

}

4 信号量与缓冲队列支持下的CAN总线驱动

前面介绍了μC/OS-II内核下多任务调度的关键技术、中断与PC体系下中断的一般方法。又以82C59A的中断5(IRQ5)、0x0D中断向量为例,介绍了中断服务子程序的重新分配和响应SJA1000控制器收发的中断服务子程序。

下面介绍信号量配合下的环形缓冲队列与中断处理程序之间的关系问题,这也是设备驱动部分的核心内容。

ERTOS的驱动程序与其它操作系统有所不同。比如Windows、Unix、Solaris、Linux等操作系统弱化了设备的概念,用户进程对设备的使用可以通过文件系统来完成。然而,在μC /OS-II上开发CAN总线驱动程序没有那么严格,只要满足设备在连续的CPU时间上使用时不发生时间重叠就可以了。

串行设备或者其它字符型设备都存在外设处理速度和CPU速度不匹配的问题,所以需要建立相应的缓冲区。向CAN口发送数据时,只要把数据写到缓冲区,然后由SJA1000控制器逐个取出往外发。从CAN口接收数据时,往往等收到若干个字节后才需要CPU进行处理,所以这些预收的数据可以先存于缓冲区。缓冲区可以设置收到若干个字节后再中断CPU,这样避免了因为CPU的频繁中断而降低系统的实时性。

在对缓冲区读写的过程中,经常会遇到想发送数据时,发送缓冲已满;想去读时,接收缓冲却是空的。对于用户程序端,可以采用查询工作方式,即放弃无法读写的操作,然后再频繁地去尝试这个操作直到成功,这样程序效率显然降低。如果引入读、写两个信号量分别对缓冲区两端的操作进行同步,问题将迎刃而解。用户任务想写但缓冲区满时,在信号量上睡眠,让CPU运行别的任务,待ISR从缓冲区读走数据后唤醒此睡眠的任务;类似地,用户任务想读但缓冲区空时,也可以在信号量上睡眠,待外部设备有数据来了再唤醒。由于μC/OS-II的信号量提供了超时等待机制,CAN口当然也具有超时读写能力。