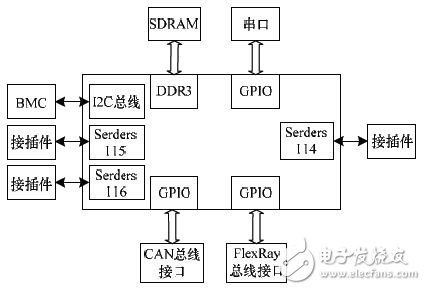

图6 总线接口单元功能组成框图

3.2 车电总线接口设计

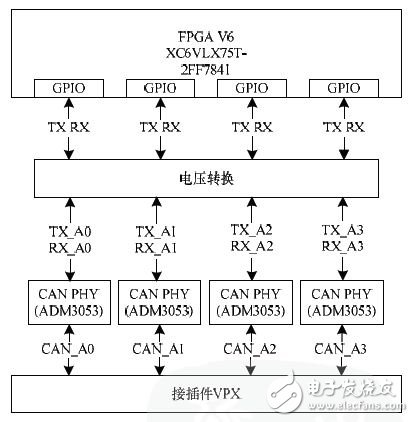

3.2.1 CAN总线接口设计

单元模块通过FPGA输出四路GPIO信号,GPIO连接电压转换芯片以完成电平转换,CAN总线信号完成电平转换后连接CAN芯片,从而输出CAN总线信号与总线接口单元VPX接插件相连,如图7所示。

图7 CAN总线接口硬件组成原理

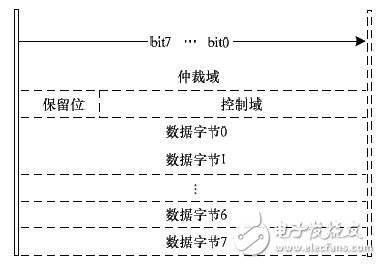

CAN帧时,处理器驱动在内存定义并组织一个下图结构体,使用RapidIO中NWRITE-R事务,写入FPGA控制器CAN发送缓冲区地址,即刻完成发送;当CAN控制器完成发送后,将对该处理器产生中断,告知发送结果。

当接收CAN帧时,处理器驱动在内存定义一个上图结构体,并将内存地址使用Rapid IO中NWRITE-R事务,写入FPGA控制器CAN接收缓冲区地址;当CAN控制器接收完一帧后,通过NWRITE-R事务写入对该处理器地址空间中并产生中断,告知发送结果。图8是内存数据结构。

图8 CAN内存数据结构

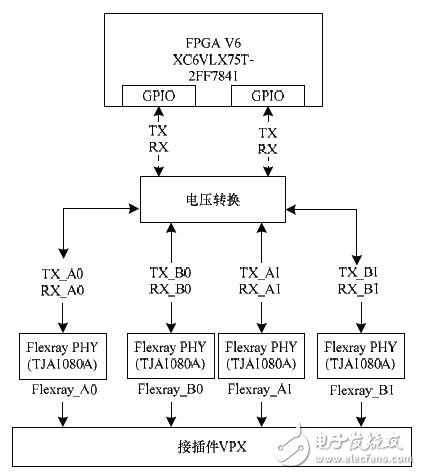

3.2.2 FlexRay总线接口设计

单元模块通过FPGA输出两路GPIO信号,GPIO连接电压转换芯片以完成电平转换,FlexRay总线信号完成电平转换后各输出两路连接FlexRay收发器。由于该XILINX核中只支持FlexRay单信道,因此选择两路FlexRay信道形成冗余设计,2组信道都分为A、B2个通道,满足FlexRay双信道的要求。收发器选用TJA1080,TJA1080收发器是恩智浦公司出品的一款针对FlexRay的具有高速时间触发通讯系统的收发芯片,也是全球第一款符合FlexRay协议2.1规定的FlexRay收发器,具有高达10Mb/s的数据传输速度。每路信号分别通过JTA1080后,最终输出四路FlexRay信号,并与总线接口单元VPX接插件相连。详细结构如图9所示。

图9 FlexRay总线接口硬件组成原理

FlexRay每个数据的数据帧由帧头、有效数据段、帧尾3个部分组成。若为发送,当时间片快到时,链表控制器通过RioMaster模块发送NREAD事务包请求数据,返回的数据进入SendFIFO,由FlexRayIP读取。若为接收,当时间片到时,链表控制器提供接收的基地址,数据收到后将存放于RecvFIFO中,结合接收基地址,通过NWRITE-R写入远端内存,之后发送Doorbell使处理器产生中断。其内存数据结构如图10所示。