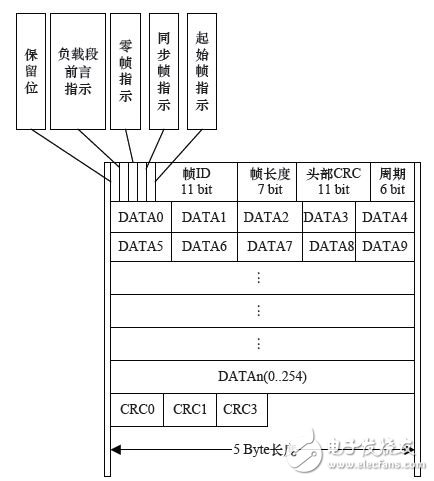

图10 FlexRay内存数据结构

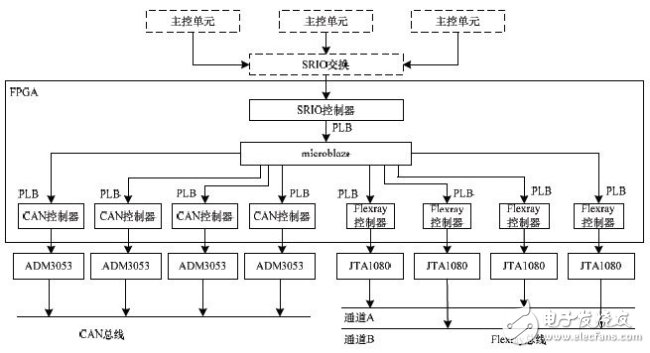

3.3 FPGA逻辑设计

本文设计通过硬件实现CAN总线控制器、FlexRay总线控制器、RapidIO总线接口等模块功能。采用Virtex6系列FPGAXC6VLX75T完成RapidIO-FlexRay、RapidIO-CAN协议转换功能。

FPGA单元包含SRIO控制器、microblaze软核及四路CAN控制器和两路FlexRay控制器。处理器将信号发送至PCIe-SRIO转接桥,经过桥芯片转换发送至SRIO交换板。交换板的一端将信号转发到SRIO控制器上,SRIO核通过PLB总线将控制信号发送至microblaze软核,经过处理信号通过PLB总线发送至四路CAN控制器和两路FlexRay控制器。每路CAN控制器均连接CAN转换器ADM3053,每路FlexRay控制器均连接FlexRay收发器JTA1080。经过转换器最终分别连接至CAN总线和FlexRay总线上。该逻辑设计的主要特点有3个:

(1)SRIO-PLB桥实现了总线接口单元模块的srio总线接入功能。

(2)CAN和FlexRay总线控制器通过板载收发器实现了CAN、FlexRay总线的接入功能。

(3)microblaze软核实现了CAN、FlexRay控制器消息和事件的预处理,完成了与SRIO总线的互连,并做了任务迁移,减轻了主控处理器的压力。

详细逻辑结构如图11所示。

图11 FPGA模块内部逻辑结构

4 仿真与验证

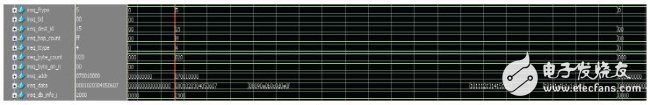

4.1 RapidIO仿真与验证

在Xilinx的ISE14.1开发环境下,基于车电总线接口单元模块对RapidIO接口进行了验证,利用ModelSim对逻辑设计进行仿真,其波形图如图12、图13所示,通过判断数据的一致性可以验证RapidIO总线接口的正确性和有效性。

图12 RapidIO数据发送时序图

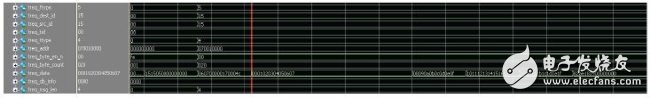

图13 RapidIO数据接收时序图

4.2 FlexRay仿真与验证

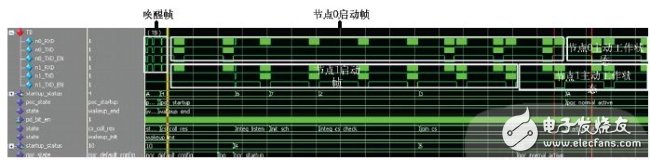

基于车电总线接口单元模块对FlexRay接口状态机制进行了验证,利用ModelSim对逻辑设计进行仿真,其波形图如图14所示。

图14 FlexRay数据收发时序图

从仿真波形中可以清楚地看出FlexRay状态机制的变化过程。当节点的收发器接收到唤醒特征符后,对主机处理器和通信控制器进行上电,唤醒并激活通信控制器、总线驱动器和总线监控器。节点0被唤醒后,将返回唤醒完成信号,并处于等待启动状态。接着节点1收到唤醒信号,返回唤醒完成信号,节点1进入启动状态,节点0也进入启动状态,最终都进入主动工作状态,开始状态机循环,显示FlexRay总线接口工作正常。