图4 两个DSP核通过两个存储体传递共享数据的例子

本文最终的优化设计表明,任意两个DSP核利用一对LOAD-STORE指令再加上一次同步操作,总共只需4拍即可完成一个共享数据字的传递,从而实现了核间细粒度共享数据的快速传输。当需要传输的共享数据量超过FSDP单通道存储容量时,可以将数据分块,进行多次传输。

除了这种对程序员透明的硬件同步机制之外,FSDP还支持基于软件查询的同步机制。即在每次改变信号灯状态前,插入一段查询“信号灯”状态的例程,然后根据查询的结果决定程序的流向。

4.4 消除读访问冲突

在FSDP的共享模式下存在多DSP核同时读一个存储体的冲突。虽然利用仲裁逻辑配合队列机制可以缓解冲突,但是,这种方式降低了FSDP的并行性。另外,可以采用存储体复制或者采用多端口存储体的方式。为此,本文进行了对比实验,结果表明,4个1KB大小的单端口SRAM在工作频率和面积上都优于4端口1KB的全定制SRAM模块,而且单端口SRAM可以由EDA工具快速编译生成,便于设计实现。因此,对于FSDP这类小容量的便笺存储器,本文采用存储体复制的方式解决访问冲突:将原来的每个存储体换成4个同样大小的单端口存储体,构成具有4个虚拟端口的存储体,如图5所示。

在处理读写访问时,存控逻辑自动进行数据写复制和读端口的分配工作,读写过程中对用户都是透明的。这种方式完全消除了多核的读访问冲突,实现了最大的共享访问带宽,提高了FSDP的并行性和实时性。

图5 存储体复制构成虚拟多端口存储体

5. 性能分析

5.1 分析模型与设计实现

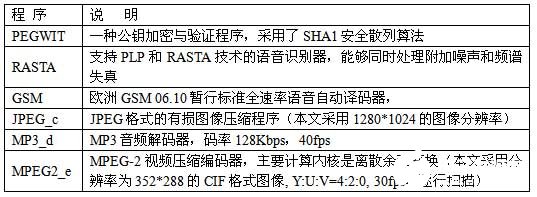

本文构建了整个SDSP的C语言模拟器SDSP-Sim。SDSP-Sim是一个时钟精确的模拟器,能够运行经过编译和手工分配的多核DSP应用程序,报告程序运行的各种统计信息和计算结果。每个处理器核占用一个模拟进程,RISC与DSP核之间采用进程通信的方式传输控制信息。本文以MediaBench基准程序集为基础,选择了6组典型的多媒体类与通信类应用程序,用于评测FSDP的性能,如表1所示。为了满足多核DSP的并行计算需求,对于原来复杂度较低的一些测试程序,例如PEGWIT和JPEG_c,本文扩大了它们的数据集。对于MP3解码程序MP3_d则将其扩展为两路并行解码器2MP3_d。由于SDSP的并行编译器开发工作还没有完成,本文仍采用手工的方式对测试程序进行并行化映射。

表1 用于性能评测的测试程序说明