Logic 逻辑

Clock signal 时钟信号

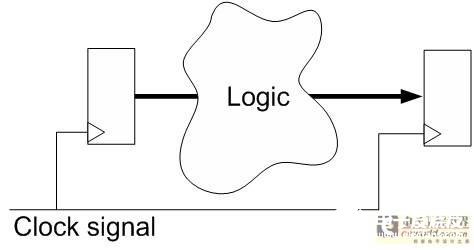

对于异步 DSP 核心,逻辑阶段被调整以消除时钟。下图显示了这种DSP 架构的基本构造。不是由时钟控制门闩线路,而实际上是传递了一个完成信号给下一逻辑阶段。根据逻辑云所执行的操作,在恰当时候可生成完成信号。

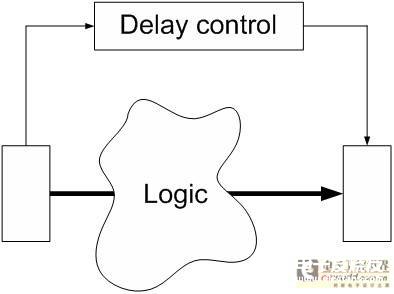

这种本地延迟控制可以保证电路的稳定。由于控制电路时间的逻辑就在本地,它就可以相应地改变电压、处理速度和温度。

Delay control 延时控制

Logic 逻辑

异步设计有许多种不同的途径,而前提是电路不受单一时钟控制。多数情况下,异步逻辑被用于通过专门的电路设计来解决具体问题。但是,异步逻辑也可用作完整 DSP 核心的基础,而不仅仅是设计中偶尔需要的一种工具。其好处包括降低功耗、可靠性提高以及电磁干扰 (EMI) 低。

异步设计的好处

采用异步设计的理由非常吸引人。在正确使用中,这种方法可以实现更低的能耗、更好的 EMI 性能;由于消除了全球时钟偏差,真正地简化了设计。

功耗更低:与同步 DSP 核心相比,异步 DSP 最重要的好处就是功耗更低。事实上,这种异步核心的能效数量级高于最好的同步DSP。

随着硅产品尺寸的缩小,功耗问题越来越重要。由于线路长度为线性而面积为平方,单位面积硅功耗将随着尺寸的缩减而增加。目前,通过降低电压,数字设计人员已经成功地解决了这个问题;但由于电压阈值的限制,目前的半导体技术无法再有效地降低电压。要想有效地利用新增加的功能,必须降低各个功能的功耗。

在CMOS 技术中,门电路切换状态时将消耗能量。在同步电路中,时钟需要进行多次切换,从而造成功耗。在设备或者设备的分区中分配时钟需要时钟缓冲器。时钟缓冲器必须足够大,以确保最大限度降低时钟偏差。换言之,电路中的所有点必须同时接受时钟变换。时钟分配通常被称为时钟树(Clock Tree),一般会消耗几乎一半的总系统能量。树底部的时钟缓冲器具有相当大的扇出量和很大的体积,因此功耗较高。

目前开发有多种技术消除切换逻辑的能耗,如时钟门控。迄今为止,这些技术都无法实现异步设计的更低功耗。

时钟门控对于异步电路来说并非必备。实际上,异步电路仅在执行有效操作时耗能。换言之,无需增加电路的情况下,异步电路的功耗将根据所提供的性能相应地增加。这意味着,不需要更多调整,这种设备就拥有低待机电流,其功耗也将随实际提供的性能而增加。