切换性能更出色:除了功耗更低外,含有异步逻辑的设备还将拥有极低的 EMI。无论是 IC 设计人员还是最终用户,它带来的好处数 不胜数。

全球或当地时钟是影响 EMI 的一个最大因素。由于同步电路中的全球时钟需要同时随处进行切换,因此同步设备所发出的 EMI 在特定频率时将拥有相当明显的峰值。

高速设备所发出的 EMI 噪音将进入 PCB 的电源层。随后该噪音将出现在外部 I/O 或布线中,在线缆中引起多余且通常超标的辐射。第一道防线采用解耦电容,而更昂贵的屏蔽或共模扼流线圈将用作最后一道防线。

电源层上的 EMI 也使得电源的设计更加复杂。对于高速运转的同步电路,电源必须经过过滤或过量储备,以符合电源层上所产生的电压尖脉冲。

这些噪音和电源问题加在一起,增加了设计人员的设计难度,尤其在特定设计中使用大量高速 DSP 时。通过消除对于全球同步时钟的需要,异步逻辑设计可以减轻或解决这些问题。可以显着地降低 EMI,使 PCB 设计更简单并提高系统的可靠性。异步电路电源波纹的缺失相当引人注目,它表明可以获得更好的切换性能。

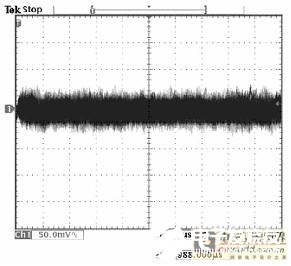

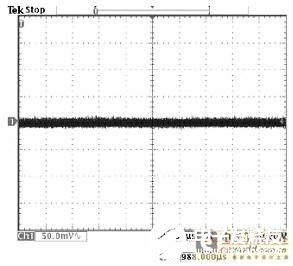

下列图显示了同步和异步 DSP 电源噪音之间的典型差异。这些图是示波器的屏幕截图,测量了高性能 DSP 在电源层上产生的噪音。

图 1:同步 DSP 电压波纹

图 2:异步 DSP 电压波纹

在 IC 设计人员眼中,更出色的切换性能代表更可靠的电路。电路同时发生大规模切换时,将产生非常大的瞬时电流。在设备的电网上显示为 IR 降。这意味着电网的某一区域在此时的电压较低。这是意料之中的正常情况,通常都通过设计验证来确保电网能承受预计的最大电压下降。有时这也是一种限制因素,妨碍设计人员在逻辑的特定区域进行进一步设计。

消除时钟偏差:采用异步设计还有很多原因。低于 90 纳米的硅片是生产的趋势。这可以从硅制造商大力投入以纠正一系列问题上得以证明。他们已着手开发干涉计量学(Interferometric Metrology)等高级技术,尽量使光罩的最小特征尺寸小于当前的曝光波长。

由于这些变量会提高设备的偏差量,因此在过程中控制它们非常重要。时钟偏差被定义为时钟信号到达电路中不同点的时间差。