fS为ADC采样速率

N为光脉冲生成至返回接收期间ADC样本的数量

假设系统使用AD9094JESD204B四通道ADC的1 GHz采样速率,那么每个样本结果相当于15厘米距离。因此,系统中不能存在采样不确定性,因为任何样本不确定性都可能导致巨大的距离测量误差。传统上,LIDAR系统以并行ADC为基础,这种ADC本身提供零采样不确定性。随着接收通道的数量不断增加,功率和PCB尺寸的要求越来越严格,这些ADC类型不能很好地扩展。另一选项是使用具备高速串行输出的ADC,例如JESD204B,以解决并行ADC存在的问题。这种选项的数据接口复杂度更高,因此难以实现零采样不确定性。

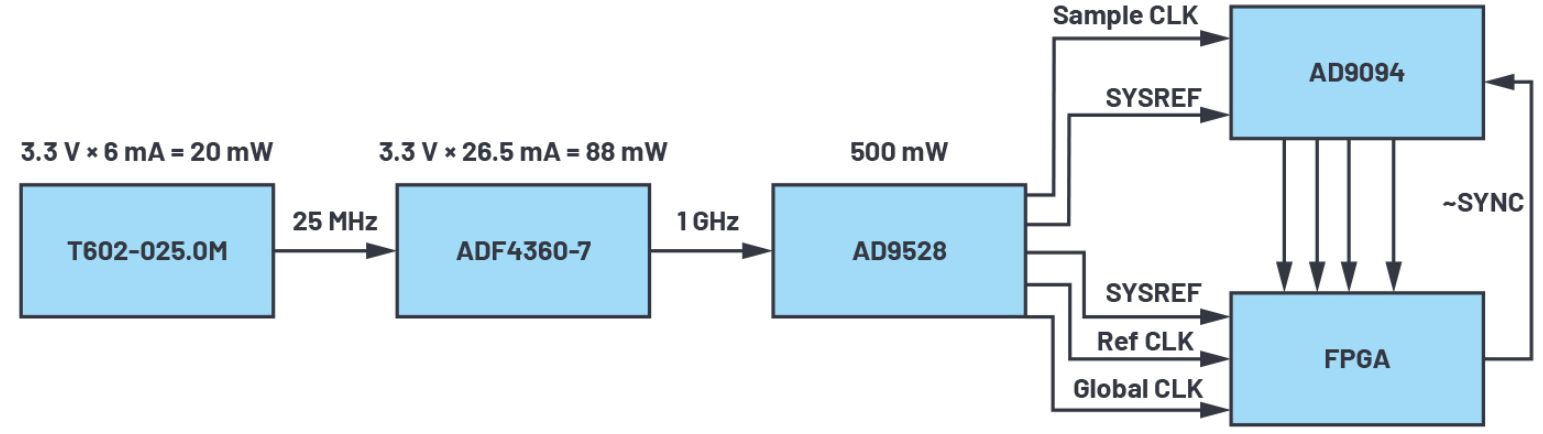

图3.DAQ板时钟和数据路径。

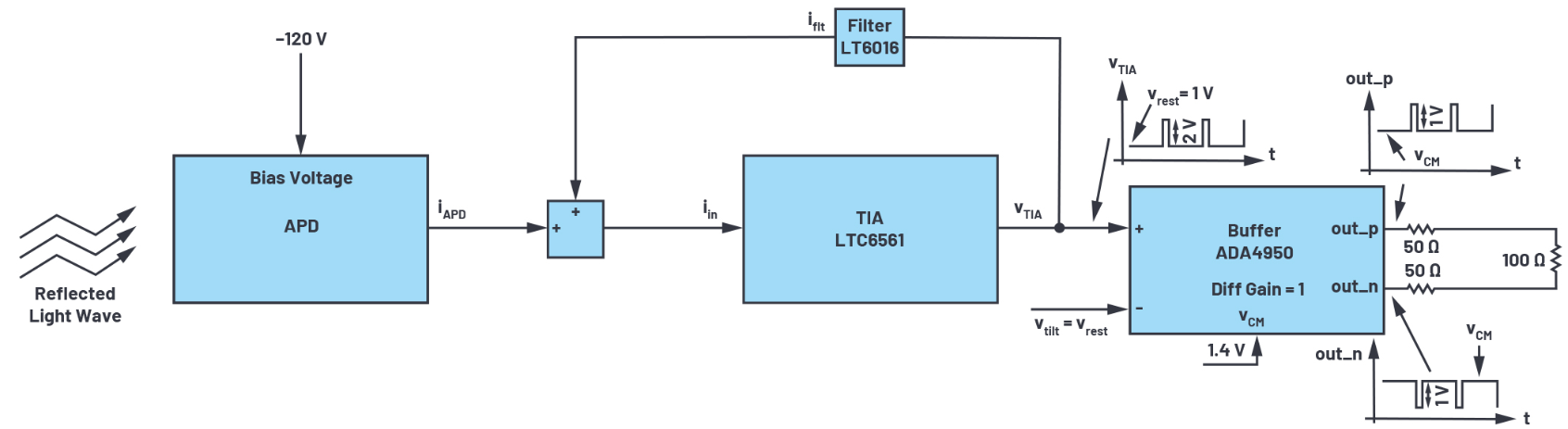

图4.AFE板信号链。

LIDAR DAQ板提供了解决这些挑战的方案,通过展示为在Subclass 1模式下运行的JESD204B数据采集系统的电源、时钟和数据接口设计来确保确定性延迟,以实现零采样不确定性,同时利用JESD204B接口提供的所有优势,令时钟方案的功耗达到最低。要在Subclass 1模式下运行JESD204B,系统总共要用到5个时钟:

►ADC采样时钟:驱动ADC信号采样过程。

►ADC和FPGA SYSREF:源同步、高压摆率时序分辨率信号,用于重置器件时钟分频器,以确保获得确定性的延迟。

►FPGA全局时钟(也称为内核时钟或器件时钟):驱动JESD204B PHY层和FPGA逻辑的输出。

►FPGA参考时钟:生成JESD204B收发器所需的PHY层内部时钟;需要等于,或是器件时钟的整数倍。

所有时钟都由一个AD9528 JESD204B时钟生成器生成,因此可以确保它们彼此都同步。 图3显示了时钟方案,以及与FPGA的数据接口。