这里的CR1S、CR1B、CR2S、CR2B是CCD输出像素的相位操作时钟。CRLAST是该CCD的信号输出时钟。RST是像素复位时钟。TCR是行转移同步信号,可用来控制转移栅。PR是曝光控制和积分时间控制信号,其电平上升沿要平滑,不能陡峭。在TCK的两个高电平之间,可由PR来控制CCD的曝光和积分时间。整个芯片的工作过程如下:当TCK的高电平到来时,CCD传感器曝光的光敏单元会将采集到的光信号转移的相应的移位单元中。CCD的光敏单元在PR积分控制信号的作用下重新开始感光积分,而进入移位单元中的信号将在两相操作时钟CR1X、CR2X的作用下移出。RST信号的作用是减小两像素之间的相关信号,可在当前像素信号输出后到下一个像素信号到来前,对残余信号进行清除。

IL-P1-4096的工作驱动时序电路如图2和图3所示。由图可见,CR1X(CR1S、CR1B)和CR2X(CR2X,CR2B)的相位必须相反,频率大小为25MHz(该频率可以根据实际使用情况和条件设定相应缩小,但所有的时序都要因此做相应改变以符合CCD的整个时序要求)。CR1X和CR2X上升沿和下降沿的时差最大不能超过5ns,CR1S和TCK时钟下降沿的时差最小不能低于5ns。TCK的频率大小为11.9kHz,理想脉宽设定为300ns。PR的频率也为11.9kHz,而脉宽则为10μs(PR的脉宽应该根据实际的使用情况适当改变大小,其高电平上升沿和TCK高电平下降沿的时差在相距23ns的基础上根据实际情况调节)。RST频率为25MHz,脉宽大小为5ns。图中的OSn(OS1、OS2)为CCD输出信号。

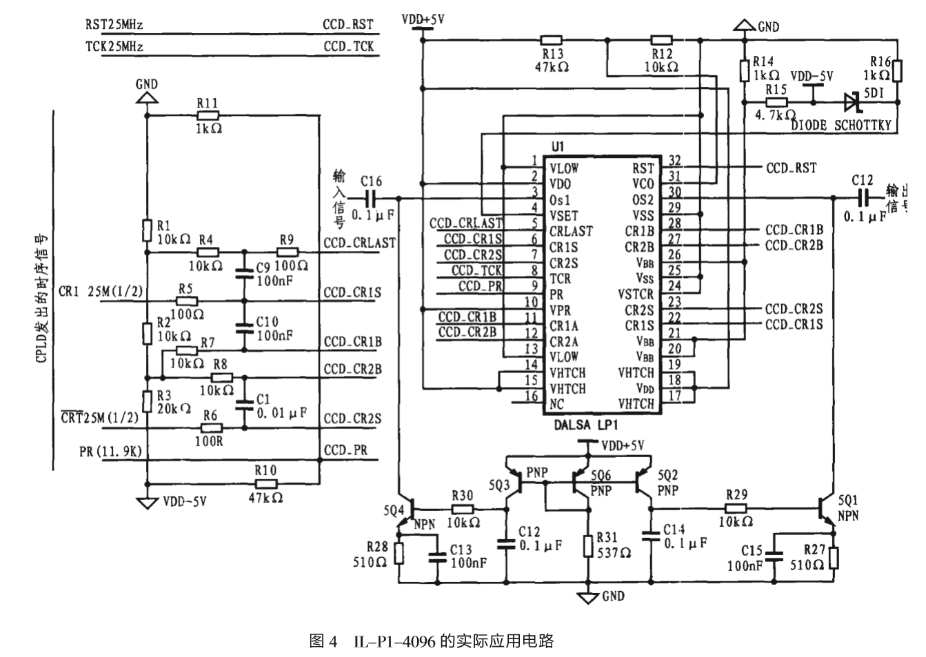

4、具体应用电路

由于对IL-PI4096的工作频率要求很高、相位关系复杂,因此,笔者推荐使用高速CPLD作为CCD的基本时序发生器。设计时可使用Lattic公司的ispMACH4000C/B/V系列芯片,该芯片的工作时钟可以达到400MHz,完全可以满足此CCD的工作时序要求。

图4所示是IL-P1-4096的具体应用电路。从CPLD发送过来的基本时钟信号可通过简单电路进行相位校正并提供驱动电流,然后再送入CCD芯片。在Osn的输出端。电路可通过几个三极管组成的恒流源来提供CCD所需要的8mA驱动电流。

在电路板布线时,时序信号线要尽量短而且宽,有条件的地方应使用伴生线。CPLD和IL-P1-4096要尽可能靠近。电路板最好使用四层板。板上电源应远离芯片和时序信号线。直流电源的纹波最好不要超过10mV。

在调式电路的时候,应当选用比较低的频率来控制IL-P1-4096的工作,然后,逐渐升高工作频率。在CPLD上使用ISP软件改变输出频率是比较方便的。